### ANALOG INTEGRATED LOCK-IN AMPLIFIER FOR OPTICAL SENSORS

João Alberto de França Ferreira

Dissertação de Mestrado apresentada ao Programa de Pós-graduação em Engenharia Elétrica, COPPE, da Universidade Federal do Rio de Janeiro, como parte dos requisitos necessários à obtenção do título de Mestre em Engenharia Elétrica.

Orientador: Antonio Petraglia

Rio de Janeiro Setembro de 2016

### ANALOG INTEGRATED LOCK-IN AMPLIFIER FOR OPTICAL SENSORS

João Alberto de França Ferreira

DISSERTAÇÃO SUBMETIDA AO CORPO DOCENTE DO INSTITUTO ALBERTO LUIZ COIMBRA DE PÓS-GRADUAÇÃO E PESQUISA DE ENGENHARIA (COPPE) DA UNIVERSIDADE FEDERAL DO RIO DE JANEIRO COMO PARTE DOS REQUISITOS NECESSÁRIOS PARA A OBTENÇÃO DO GRAU DE MESTRE EM CIÊNCIAS EM ENGENHARIA ELÉTRICA.

Examinada por:

Prof. Antonio Petraglia, Ph.D.

Prof. Marcelo Martins Werneck, Ph.D.

Prof. João Carlos Machado, Ph.D.

RIO DE JANEIRO, RJ – BRASIL SETEMBRO DE 2016 Ferreira, João Alberto de França

Analog Integrated Lock-In Amplifier for Optical Sensors/João Alberto de França Ferreira. – Rio de Janeiro: UFRJ/COPPE, 2016.

XVII, 86 p.: il.; 29,7cm.

Orientador: Antonio Petraglia

Dissertação (mestrado) – UFRJ/COPPE/Programa de Engenharia Elétrica, 2016.

Referências Bibliográficas: p. 79 – 84.

1. Analog lock-in amplifier. 2. Fiber optic 3. CMOS analog integrated circuit. sensor. Low-voltage low-power integrated sensor system. 4. 5.Transimpedance amplifier (TIA). 6. Operational transconductance amplifier (OTA). I. Petraglia, Antonio. II. Universidade Federal do Rio de Janeiro, COPPE, Programa de Engenharia Elétrica. III. Título.

# Acknowledgment

I would like to thank my advisor, professor Antonio Petraglia, for suggesting this work theme, that enabled me to gain expertise and practice in the design of analog integrated circuits, for his support and comprehension.

I would also like to thank all other professors of the PADS laboratory, professors Fernando Antônio Pinto Barúqui, José Gabriel Rodriguez Carneiro Gomes, Carlos Fernando Teodósio Soares and Mariane Petraglia, for the exchanges and support and professors Antonio Carneiro de Mesquita Filho e Antonio Carlos Moreirão de Queiroz, for the classes in interesting topics.

I express my gratitude with all the friends of the PADS laboratory for the friendship and help throughout this time, nominaly, Allan Bides and Luiza, Eduardo Anjos, Fernanda Duarte, Luis Fabián, Genildo Nonato, Odair, Juan Pablo Giron and Ana, Fabio de Lacerda, Thiago Brito, Mauro, Felipe Petraglia, Fellipe Falleiro, Thiago Valentim, Florian Wolf, Humberto Paz, Pedro Riascos, Edgard, Roberto, Francinei, Jorge de La Cruz, Oscar Palacios, Motta, Rafael and Manoel.

I shall mention the generous offer of the IEN (Instituto de Energia Nuclear) that enabled the PADS laboratory students to use its LPKF prototyping machine to manufacture their test boards. The visits to the IEN, the tasks develop there and all the exchanges with Fabio were very motivating. Resumo da Dissertação apresentada à COPPE/UFRJ como parte dos requisitos necessários para a obtenção do grau de Mestre em Ciências (M.Sc.)

### AMPLIFICADOR LOCK-IN ANALÓGICO INTEGRADO PARA SENSORES ÓPTICOS

João Alberto de França Ferreira

Setembro/2016

Orientador: Antonio Petraglia

Programa: Engenharia Elétrica

Este trabalho propõe uma topologia de amplificador lock-in analógico integrado para sensores ópticos. Um protótipo foi desenvolvido visando a sua utilização em um sensor a fibra óptica plástica para a medição do índice de refração de um meio aquoso. O projeto objetivou a integração em silício de todos os componentes do sistema e a geração de um circuito de baixa potência e baixa tensão, de maneira a viabilizar sua utilização em aplicações portáteis. A topologia do amplificador apresenta entradas e saídas diferenciais para mitigar problemas com ruído e interferências. O protótipo foi implementado em uma tecnologia CMOS 0,18 micrômetros. Foi utilizada uma tensão de alimentação unipolar de 1,8 volts. Simulações pós-layout indicam que o sistema pode operar com sinais num intervalo de frequências entre 100 Hz e 2 KHz, é capaz de rejeitar a componente DC da fotocorrente que tenha uma magnitude de até 10  $\mu$ A e consegue processar com precisão sinais de até 14  $\mu$ A de amplitude, com um consumo estático de potência de 275  $\mu$ W.

Abstract of Dissertation presented to COPPE/UFRJ as a partial fulfillment of the requirements for the degree of Master of Science (M.Sc.)

### ANALOG INTEGRATED LOCK-IN AMPLIFIER FOR OPTICAL SENSORS

João Alberto de França Ferreira

September/2016

Advisor: Antonio Petraglia

Department: Electrical Engineering

This work proposes a topology for an analog integrated lock-in amplifier for fiber optic sensors. A prototype has been developed for application in a plastic optical fiber sensor for measuring the refractive index in an aqueous medium. The design aimed at the integration of all system components in silicon and the generation of a low power and low voltage circuit, to allow its use in portable applications. The amplifier topology features differential inputs and outputs to mitigate problems with noise and interference. A prototype was implemented in a 0.18 microns CMOS technology. A unipolar power supply of 1.8 volts was used. Post-layout simulations indicate that the system can operate with signals in a frequency range between 100 Hz and 2 kHz, it is able to reject the DC photocurrent component with a magnitude of up to 10  $\mu$ A and can accurately process signals up to 14  $\mu$ A of amplitude, with a static power consumption of 275  $\mu$ W.

# Contents

| Li            | st of                          | Figures                                            |   | ix   |  |  |

|---------------|--------------------------------|----------------------------------------------------|---|------|--|--|

| $\mathbf{Li}$ | st of                          | Tables                                             |   | xiii |  |  |

| $\mathbf{Li}$ | st of                          | symbols                                            |   | xiv  |  |  |

| $\mathbf{Li}$ | st of                          | abbreviations                                      |   | xvi  |  |  |

| 1             | Intr                           | roduction                                          |   | 1    |  |  |

|               | 1.1                            | Lock-in amplifier                                  |   | 3    |  |  |

|               | 1.2                            | Motivation and objectives                          |   | 4    |  |  |

|               | 1.3                            | Literature review                                  |   | 5    |  |  |

| <b>2</b>      | System Level Analysis 10       |                                                    |   |      |  |  |

|               | 2.1                            | Considerations on signals and noise                |   | 11   |  |  |

|               |                                | 2.1.1 Noise                                        |   | 12   |  |  |

|               |                                | 2.1.2 Signal-to-noise ratio                        |   | 13   |  |  |

|               |                                | 2.1.3 Broadband noise                              |   | 14   |  |  |

|               |                                | 2.1.4 Low-frequency noise                          |   | 16   |  |  |

|               | 2.2                            | Filtered noise and noise bandwidth                 |   | 17   |  |  |

|               | 2.3                            | Signal spectrum and modulation                     |   | 19   |  |  |

|               | 2.4                            | Fundamentals of lock-in systems                    |   | 21   |  |  |

|               | 2.5                            | Lock-in amplifier architecture                     |   | 26   |  |  |

|               | 2.6                            | Sizing methodology                                 | • | 28   |  |  |

| 3             | Circuit Design and Analysis 31 |                                                    |   |      |  |  |

|               | 3.1                            | Initial considerations about the technology        |   | 31   |  |  |

|               | 3.2                            | DC photocurrent rejection circuit                  |   | 33   |  |  |

|               |                                | 3.2.1 Operational transconductance amplifier (OTA) | • | 36   |  |  |

|               | 3.3                            | Transimpedance amplifier (TIA)                     |   | 37   |  |  |

|               |                                | 3.3.1 Operational amplifier                        |   | 38   |  |  |

|               | 3.4                            | Mixer                                              |   | 39   |  |  |

|                                                                                                               | 3.5          | Low-pass filter                                                    | 40 |  |

|---------------------------------------------------------------------------------------------------------------|--------------|--------------------------------------------------------------------|----|--|

|                                                                                                               |              | 3.5.1 Operational transconductance amplifier (OTA)                 | 43 |  |

| 4                                                                                                             | Laye         | out                                                                | 47 |  |

|                                                                                                               | 4.1          | Layout techniques                                                  | 48 |  |

|                                                                                                               | 4.2          | Transimpedance amplifier                                           | 49 |  |

|                                                                                                               | 4.3          | Mixer                                                              | 51 |  |

|                                                                                                               | 4.4          | Low-pass filter                                                    | 51 |  |

|                                                                                                               | 4.5          | Lock-in amplifier                                                  | 53 |  |

|                                                                                                               | 4.6          | Integrated circuit                                                 | 54 |  |

| <b>5</b>                                                                                                      | Sim          | ulation Results                                                    | 58 |  |

|                                                                                                               | 5.1          | Transimpedance amplifier                                           | 58 |  |

|                                                                                                               | 5.2          | Mixer                                                              | 61 |  |

| 5.3 Low-pass filter $\ldots$ |              |                                                                    | 63 |  |

|                                                                                                               | 5.4          | -                                                                  |    |  |

|                                                                                                               |              | 5.4.1 Simulation under nominal conditions and without interference | 68 |  |

|                                                                                                               |              | 5.4.2 Monte Carlo simulation without interference                  | 70 |  |

|                                                                                                               |              | 5.4.3 Simulation under nominal conditions and with interference    | 72 |  |

|                                                                                                               |              | 5.4.4 Monte Carlo simulation including interference                | 74 |  |

|                                                                                                               |              | 5.4.5 Bench evaluation tests                                       | 76 |  |

| 6                                                                                                             | Con          | clusions                                                           | 77 |  |

|                                                                                                               | 6.1          | Suggestions for future works                                       | 78 |  |

| Bi                                                                                                            | Bibliography |                                                                    |    |  |

| $\mathbf{A}$                                                                                                  | TIA          | Differential Gain Derivation                                       | 85 |  |

# List of Figures

| 1.1 | Structure of a fiber optic sensor, with a light source to generate an                                                |    |

|-----|----------------------------------------------------------------------------------------------------------------------|----|

|     | optical reference, an optical fiber and transductor, where the optical                                               |    |

|     | reference will be modulated accordingly to a physical property whose                                                 |    |

|     | magnitude is desired, an optical detector to convert the optical signal                                              |    |

|     | to an electrical signal and a conditioning and processing circuit where                                              |    |

|     | the signal is demodulated. $\ldots$ | 2  |

| 1.2 | Block diagram of an analog two-phase lock-in amplifier (optional com-                                                |    |

|     | ponents are enclosed in a dashed box) comprising an amplification                                                    |    |

|     | path, two synchronous demodulators, each one consisting of the in-                                                   |    |

|     | phase and quadrature channels, and a reference signal path that gen-                                                 |    |

|     | erates an appropriate reference for the demodulators                                                                 | 4  |

| 2.1 | Example of the PSD of a voltage $(S_{v}(f))$ and current $(S_{i}(f))$ signals,                                       |    |

|     | showing the dominance of flicker noise at frequencies below the corner                                               |    |

|     | frequency $f_c$ , and the dominance of thermal noise at frequencies above                                            |    |

|     | $f_c$                                                                                                                | 13 |

| 2.2 | Example of the amplitude spectral density of a voltage $(S_v^{\frac{1}{2}}(f))$ and                                  |    |

|     | current $(S_i^{\frac{1}{2}}(f))$ signals demonstrating the dominance of flicker noise                                |    |

|     | at frequencies below the corner frequency $f_c$ , and the dominance of                                               |    |

|     | thermal noise at frequencies above $f_c$                                                                             | 13 |

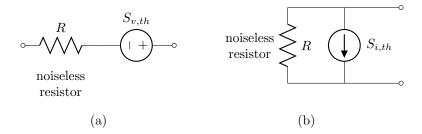

| 2.3 | Models for a noisy resistor                                                                                          | 15 |

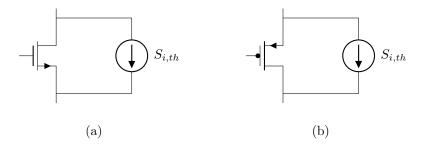

| 2.4 | Model of a noisy (a) nmos transistor; (b) pmos transistor                                                            | 15 |

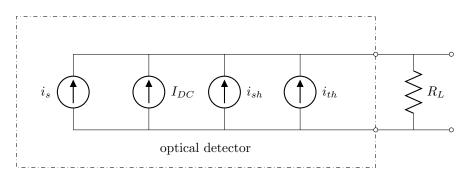

| 2.5 | Noise equivalent circuit of an optical detector and its various compo-                                               |    |

|     | nents: $i_s$ - signal current, $I_{DC}$ - bias current, $i_{sh}$ - shot noise current                                |    |

|     | and $i_{th}$ - thermal noise current                                                                                 | 16 |

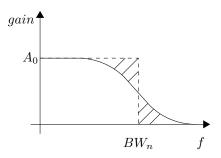

| 2.6 | Noise bandwidth $BW_n$ and its comparison to the bandwidth of a                                                      |    |

|     | practical filter                                                                                                     | 18 |

| 2.7 | Spectrum magnitude of signal $m(t)$ (above) and the spectrum of                                                      |    |

|     | the same signal modulated by a sinusoidal carrier of frequency $\omega_0$ and                                        |    |

|     | amplitude $A_c$ (below)                                                                                              | 20 |

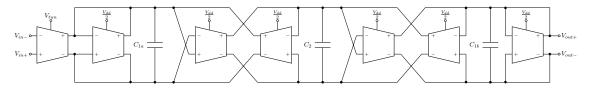

| 2.8 | Proposed topology for a single-phase lock-in amplifier                                                               | 27 |

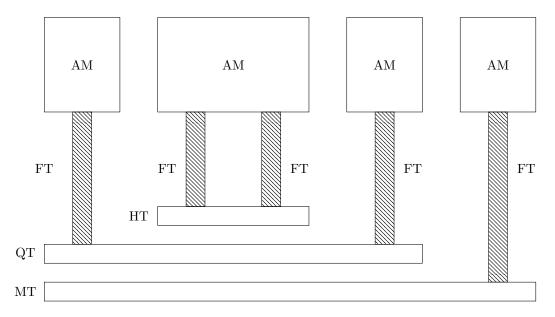

| 3.1  | Sectional view of a dual MIM capacitor. AM is the thick aluminum                                 |    |

|------|--------------------------------------------------------------------------------------------------|----|

|      | metal, FT is a square via that connects AM to MT and the capacitor                               |    |

|      | plates, HT and QT are capacitor plates in copper and MT is the bottom capacitor plate in copper. | 32 |

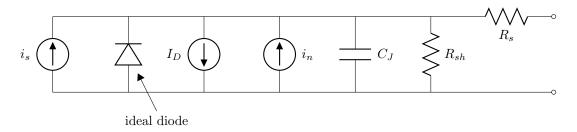

| 3.2  | Photodiode model. $i_s$ is the signal current, $I_D$ the dark current, $i_n$ a                   |    |

| 0.2  | noise current, $C_i$ the junction capacitance, $R_{sh}$ the shunt resistance,                    |    |

|      | $R_s$ the series resistance, and the ideal diode models the diode char-                          |    |

|      | acteristic of the photodiode when this is direct biased                                          | 33 |

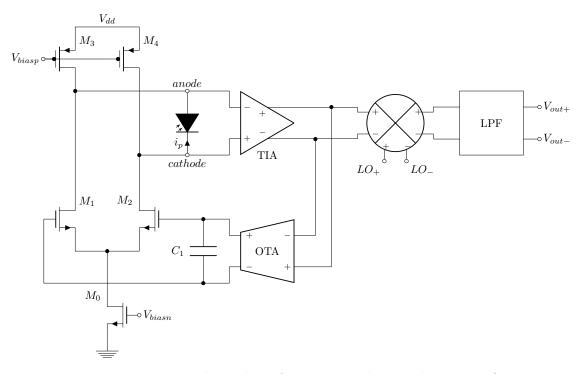

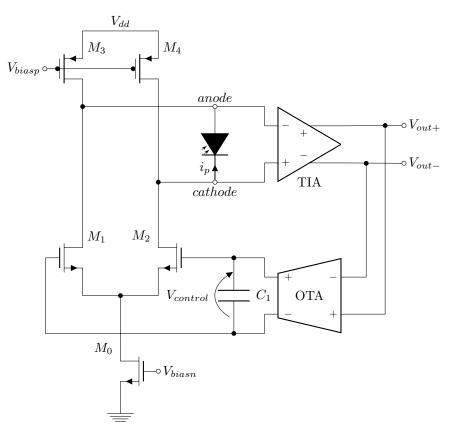

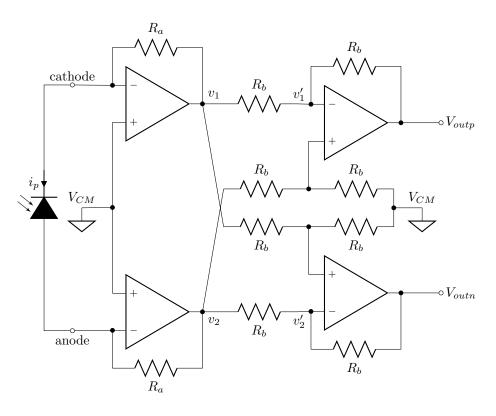

| 3.3  | DC photocurrent rejection circuit solution. The TIA amplifies the                                | 00 |

| 0.0  | photocurrent $i_p$ and the loop formed by the low-pass filter (OTA +                             |    |

|      | $C_1$ ) and $M_0 - M_4$ transistors act to reject the DC component of the                        |    |

|      | photocurrent.                                                                                    | 34 |

| 3.4  | Topology for the OTA of the DC photocurrent rejection circuit                                    | 36 |

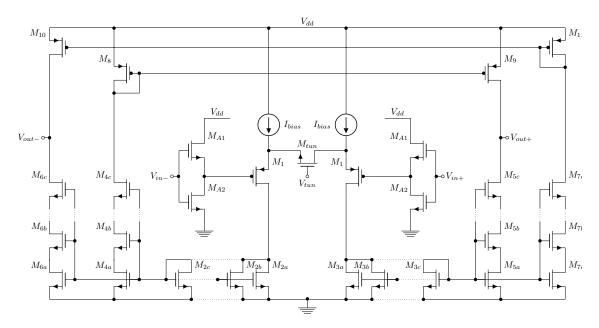

| 3.5  | Trasimpedance amplifier (TIA) topology.                                                          | 37 |

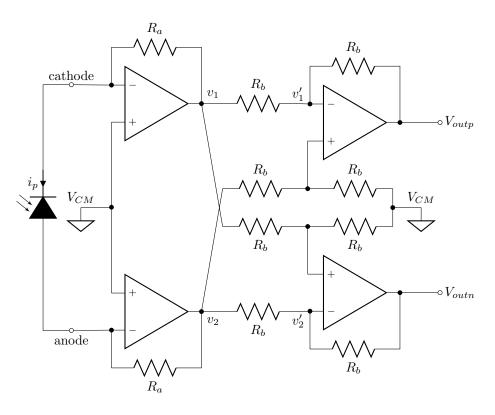

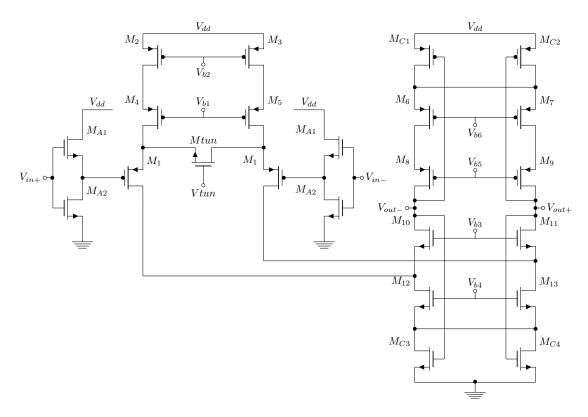

| 3.6  | Operational Amplifier topology.                                                                  | 39 |

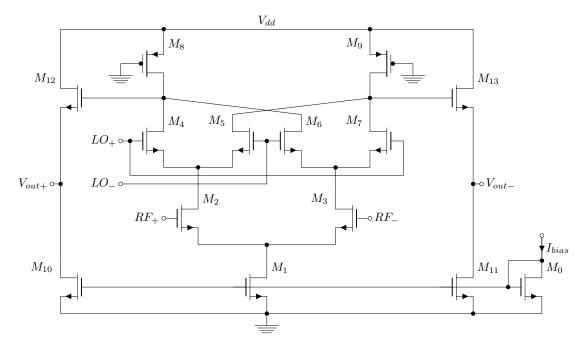

| 3.7  | Mixer topology, consisting of a Gilbert cell and an common-drain                                 |    |

|      | amplifier working as a buffer and level-shifter                                                  | 41 |

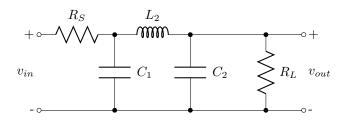

| 3.8  | LC doubly terminated ladder prototype for the low-pass filter                                    | 42 |

| 3.9  | Transconductor equivalent circuit for a resistor. $\ldots$ $\ldots$ $\ldots$ $\ldots$            | 43 |

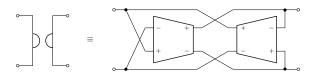

| 3.10 | A gyrator implemented by two transconductors                                                     | 43 |

| 3.11 | Third-order fully differential $G_m$ -C low-pass filter. The filter gain can                     |    |

|      | be adjusted by setting the first OTA transconductance through the                                |    |

|      | $V_{tun}$ voltage. The other OTA transconductances are fixed by setting                          |    |

|      | the $V_{tun}$ voltage to $\frac{V_{dd}}{2}$                                                      | 44 |

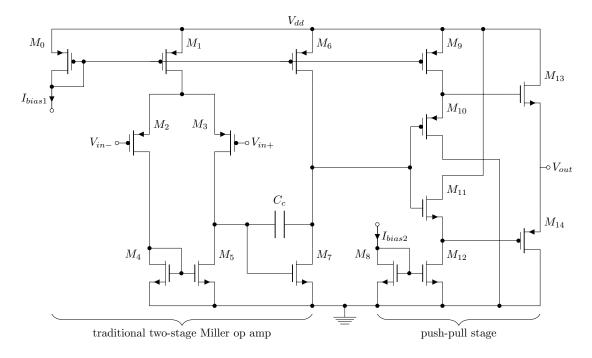

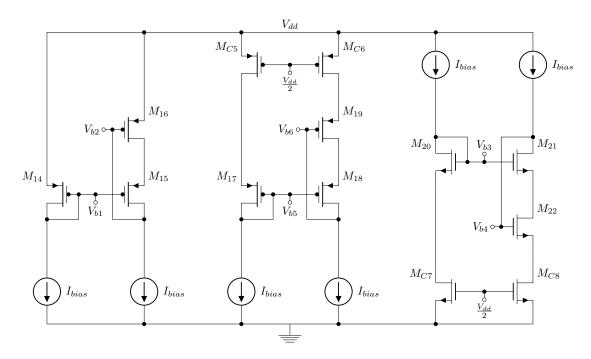

| 3.12 | Low-pass filter OTA topology, consisting of a folded-cascode with a                              |    |

|      | degeneration transistor and input attenuators                                                    | 45 |

| 3.13 | OTA bias voltages.                                                                               | 45 |

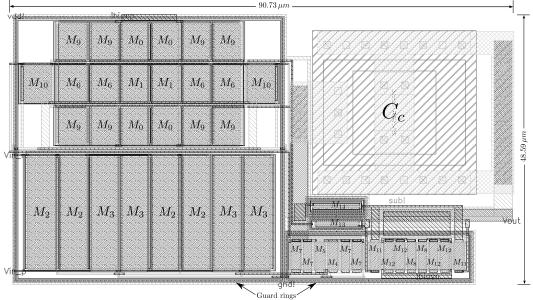

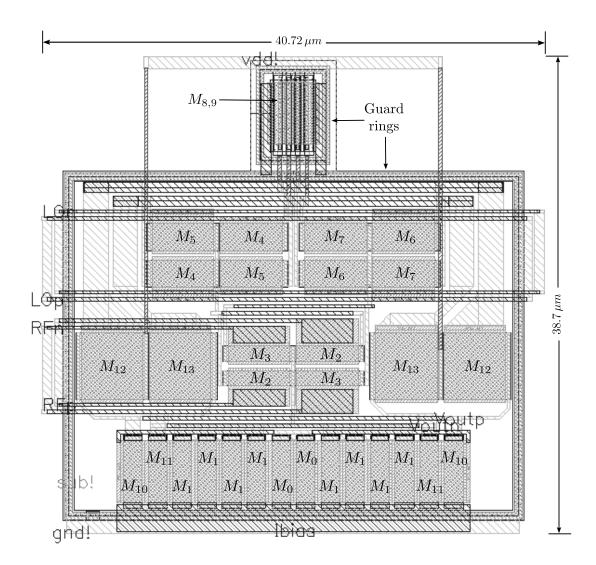

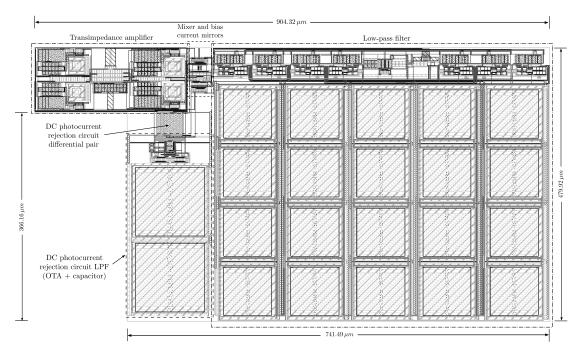

| 4.1  | Transimpedance amplifier layout.                                                                 | 49 |

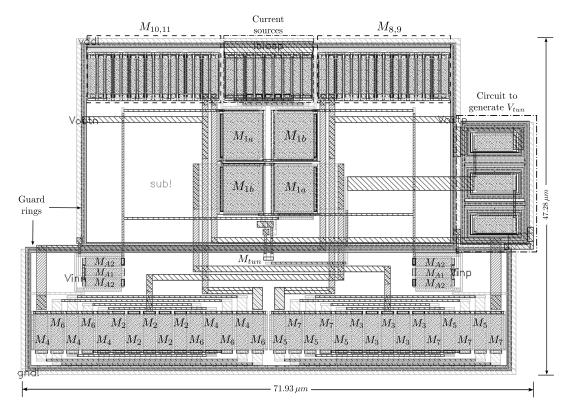

| 4.2  | Operational amplifier layout                                                                     | 50 |

| 4.3  | Mixer layout.                                                                                    | 52 |

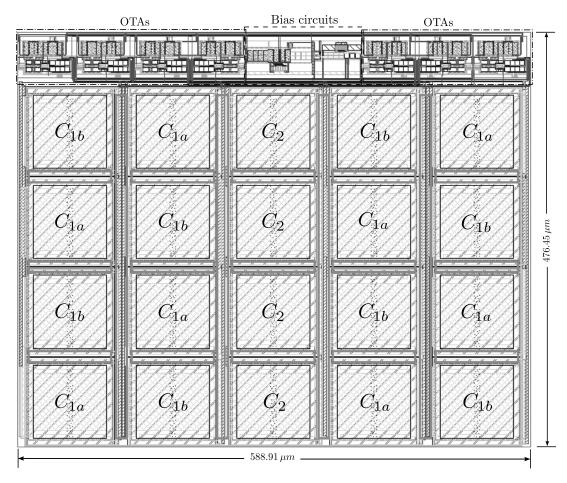

| 4.4  | Low-pass filter layout.                                                                          | 53 |

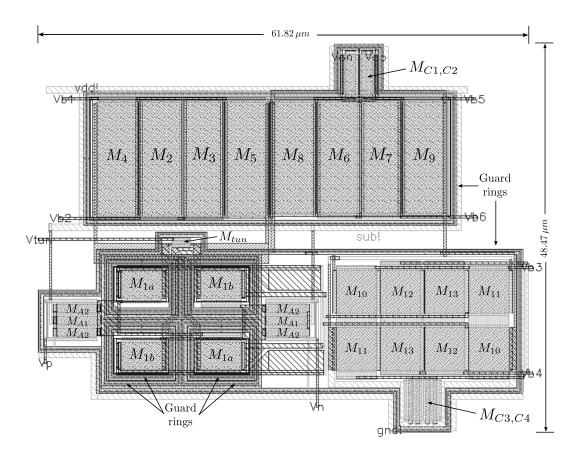

| 4.5  | Low-pass filter OTA layout.                                                                      | 54 |

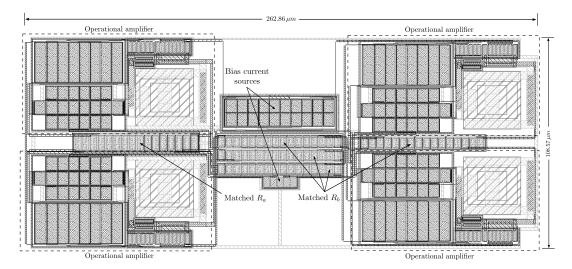

| 4.6  | Complete lock-in amplifier layout                                                                | 55 |

| 4.7  | DC photocurrent rejection circuit OTA layout                                                     | 56 |

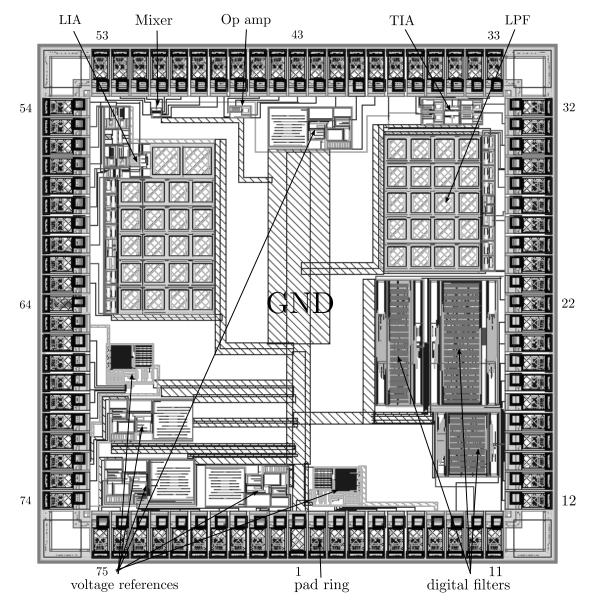

| 4.8  | Integrated circuit sent to fabrication                                                           | 57 |

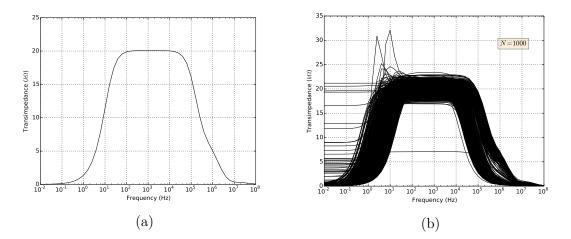

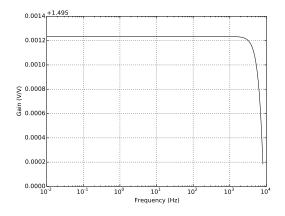

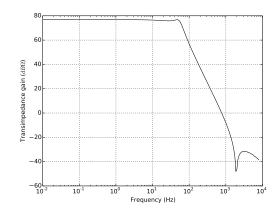

| 5.1  | Transimpedance amplifier frequency response.                                                     | 59 |

| 5.2  | Nominal (a) and Monte Carlo (b) simulation of the TIA frequency                                  |    |

|      | response within the DC photocurrent rejection circuit loop                                       | 59 |

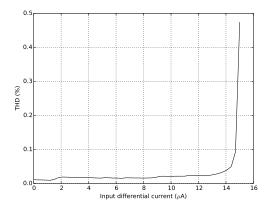

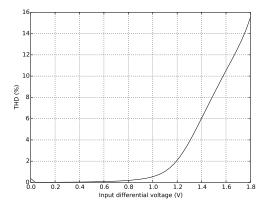

| 5.3  | Transimpedance amplifier THD                                            | 60 |

|------|-------------------------------------------------------------------------|----|

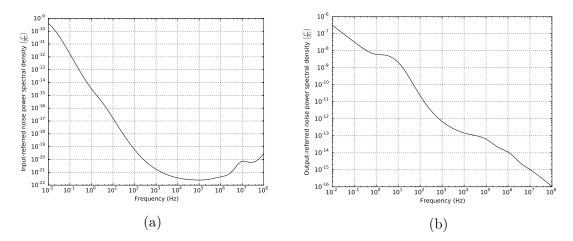

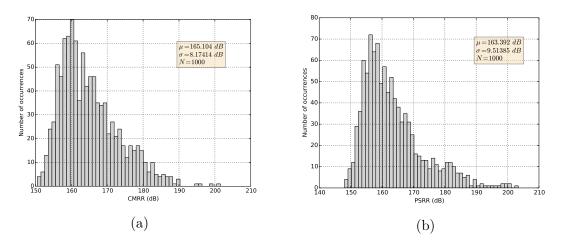

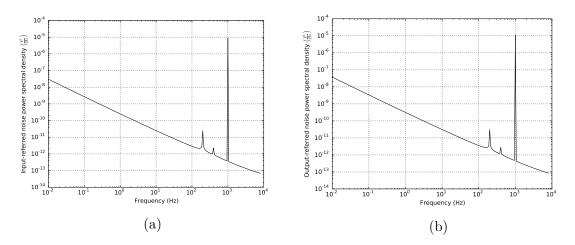

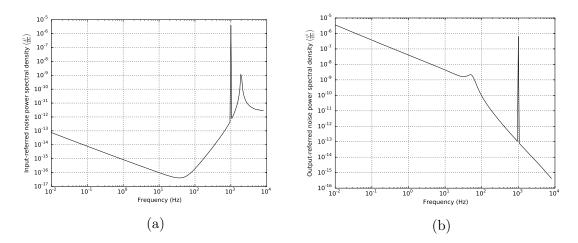

| 5.4  | Input-referred (a) and output-referred (b) noise spectral densities of  |    |

|      | the TIA, taking on account the feedback path for the rejection of the   |    |

|      | DC photocurrent.                                                        | 61 |

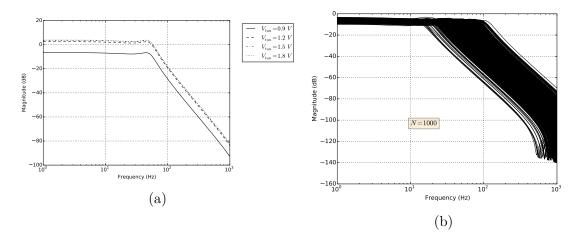

| 5.5  | Monte Carlo simulations showing the CMRR (a) and PSRR (b) values        |    |

|      | for the TIA.                                                            | 62 |

| 5.6  | Mixer gain as a function of frequency                                   | 62 |

| 5.7  | Input-referred (a) and output-referred (b) noise spectral density of    |    |

|      | the mixer                                                               | 63 |

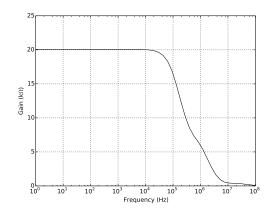

| 5.8  | Nominal frequency response of the LPF for different values of $V_{tun}$ |    |

|      | (a) and Monte Carlo simulation of the LPF frequency response for        |    |

|      | $V_{tun} = 0.9 V$ (b)                                                   | 64 |

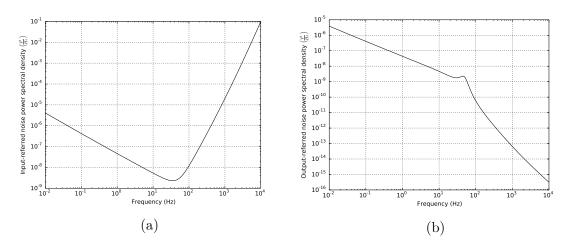

| 5.9  | Input-referred (a) and output-referred (b) noise spectral density of    |    |

|      | the low-pass filter.                                                    | 65 |

| 5.10 | Low-pass filter THD                                                     | 65 |

| 5.11 | Lock-in amplifier gain.                                                 | 66 |

|      | Input-referred (a) and output-referred (b) noise spectral density of    |    |

|      | the lock-in amplifier.                                                  | 66 |

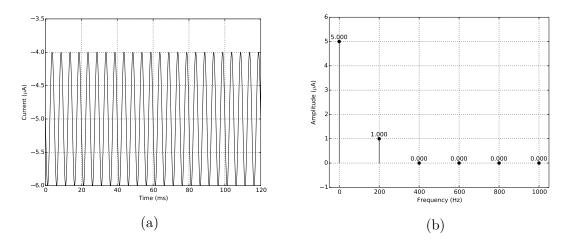

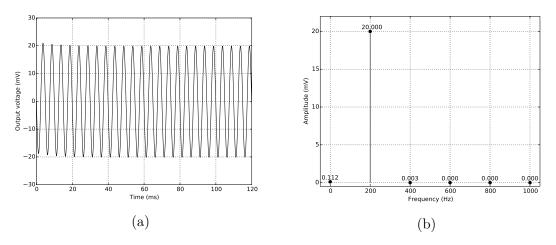

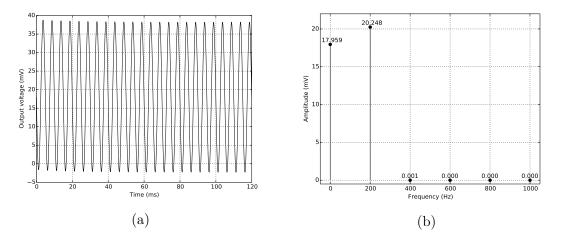

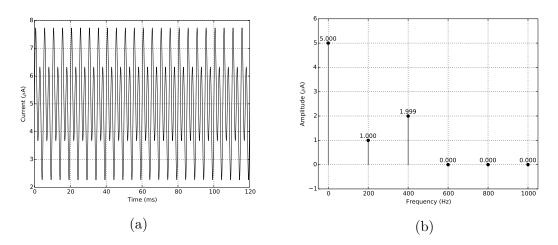

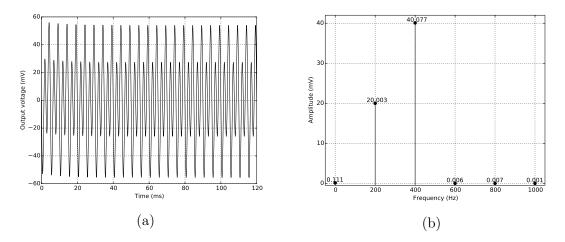

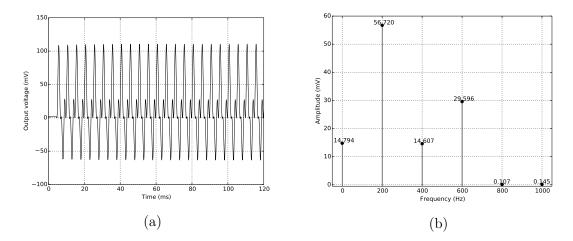

| 5.13 | Lock-in amplifier input photocurrent signal (a) and its DFT (b)         | 68 |

|      | Differential signal waveform at the TIA output (a) and its DFT (b).     | 69 |

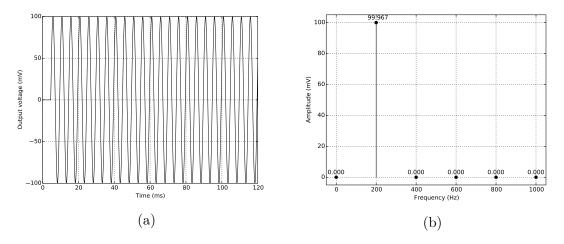

|      | LO signal (a) and its DFT (b).                                          | 69 |

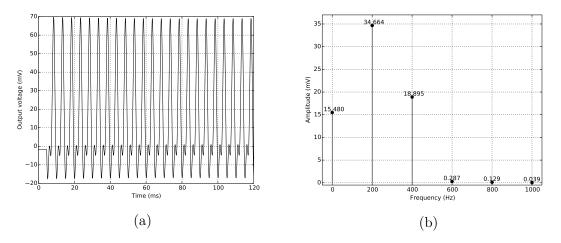

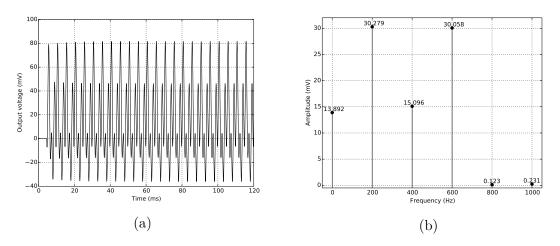

|      | Waveform at the output of the mixer (a) and its DFT (b)                 | 70 |

| 5.17 | Lock-in amplifier output signal (a) and its DFT (b)                     | 70 |

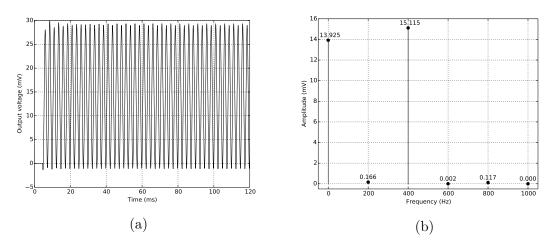

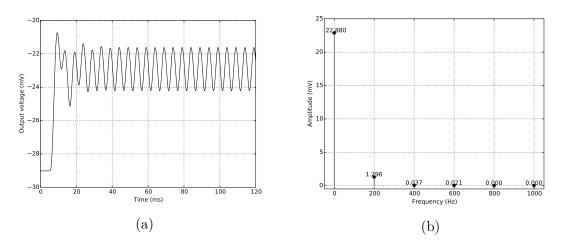

| 5.18 | Differential signal waveform at the TIA output (a) and its DFT (b).     | 71 |

| 5.19 | Waveform at the output of the mixer (a) and its DFT showing an          |    |

|      | undesired component in 200 Hz due to the TIA offset (b)                 | 71 |

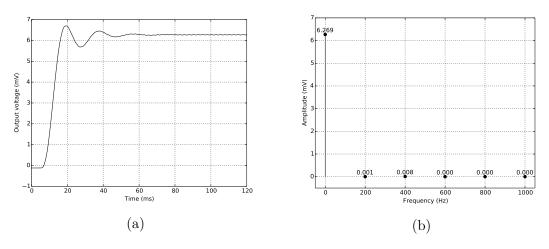

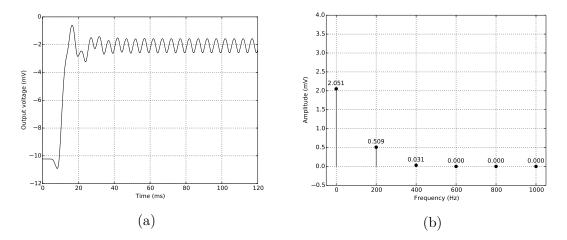

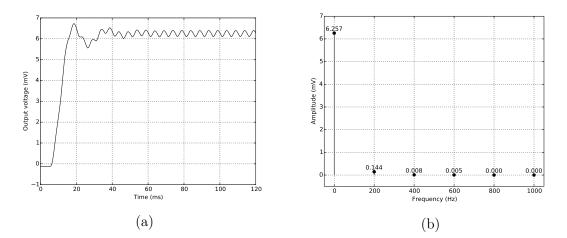

| 5.20 | Lock-in amplifier output signal (a) showing ripple and its DFT (b)      |    |

|      | presenting the magnitude of the high order components responsible       |    |

|      | for this ripple.                                                        | 72 |

| 5.21 | Lock-in amplifier input photocurrent signal superposed with a inter-    |    |

|      | ference signal at 400 Hz (a) and its DFT (b)                            | 73 |

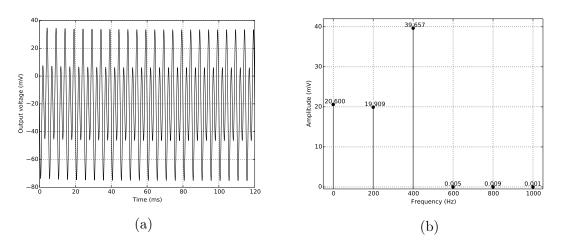

| 5.22 | Differential signal waveform at the TIA output with interference (a)    |    |

|      | and its DFT (b).                                                        | 73 |

| 5.23 | Waveform at the output of the mixer (a) and its DFT (b)                 | 74 |

| 5.24 | Lock-in amplifier output signal (a) with small ripple and its DFT (b)   |    |

|      | showing the magnitude of the high order components responsible for      |    |

|      | the ripple                                                              | 74 |

| 5.25 | Differential signal waveform at the TIA output (a) and its DFT (b)      | 75 |

| 5.26 | Waveform at the output of the mixer (a) and its DFT (b) showing an      |    |

|------|-------------------------------------------------------------------------|----|

|      | undesired component at 200 Hz owed to the translations of part of       |    |

|      | the interference and part of the DC component due to the TIA offset.    | 75 |

| 5.27 | Lock-in amplifier output signal (a) with significant ripple and its DFT |    |

|      | (b) showing the magnitude of the high order components causing the      |    |

|      | ripple                                                                  | 76 |

| A.1  | Trasimpedance amplifier (TIA) topology.                                 | 85 |

# List of Tables

| 2.1  | Sizing function parameters                                                 | 30 |

|------|----------------------------------------------------------------------------|----|

| 3.1  | Transistors dimensions of the DC photocurrent rejection circuit            | 34 |

| 3.2  | Capacitor dimensions of the DC photocurrent rejection circuit              | 35 |

| 3.3  | Transistors dimensions for the OTA of Figure 3.4                           | 37 |

| 3.4  | Transimpedance amplifier (TIA) resistors dimensions $\ldots \ldots \ldots$ | 38 |

| 3.5  | Transistors dimensions for the operational amplifier block                 | 40 |

| 3.6  | Capacitor dimensions for the operational amplifier block $\ldots$          | 40 |

| 3.7  | Transistors dimensions for the mixer block                                 | 41 |

| 3.8  | LC ladder prototype component values                                       | 43 |

| 3.9  | Low-pass filter capacitors dimensions                                      | 44 |

| 3.10 | Devices dimensions of the low-pass filter OTA                              | 46 |

| 4.1  | Integrated circuit pins mapping                                            | 56 |

| 5.1  | Parameter value for the computation of the margin of error                 | 60 |

| 5.2  | Filter low-frequency poles                                                 | 64 |

| 5.3  | Characteristics of the various designed lock-in amplifiers                 | 67 |

# List of symbols

| $A_c$                                                               | carrier amplitude, p. 19                               |

|---------------------------------------------------------------------|--------------------------------------------------------|

| $A_{m}\left(t\right)$                                               | amplitude of modulating signal, p. 19                  |

| $A_r$                                                               | reference signal amplitude, p. 21                      |

| $BW_n$                                                              | noise bandwidth, p. 18                                 |

| $C'_{ox}$                                                           | gate-oxide capacitance per unit area, p. 17            |

| K                                                                   | flicker noise process-dependent constant, p. 17        |

| L                                                                   | transistor channel length, p. 17                       |

| R                                                                   | resistance value, p. 14                                |

| $R_L$                                                               | resistive load, p. 12                                  |

| $S_{i,sh}$                                                          | shot noise power spectral density, p. 16               |

| $S_{v,th},  S_{i,th}$                                               | thermal noise power spectral density, p. 14            |

| $S_{v}\left(f\right),S_{i}\left(f ight)$                            | noise power spectral density, p. 12                    |

| $S_{v}^{\frac{1}{2}}\left(f ight),S_{i}^{\frac{1}{2}}\left(f ight)$ | noise amplitude spectral density, p. 13                |

| T                                                                   | temperature (in Kelvins), p. 14                        |

| $T_p$                                                               | (time) period; suitable averaging time interval, p. 12 |

| $V_t$                                                               | threshold voltage, p. 31                               |

| W                                                                   | transistor channel width, p. 17                        |

| *                                                                   | convolution operator, p. 21                            |

| $\delta\left(\omega ight)$                                          | Dirac delta function, p. 20                            |

| $\gamma$                                                            | white noise parameter, p. 15                           |

- $\mathscr{F}\left\{\cdot\right\}$  Fourier transform, p. 20

- $\omega_c$  carrier frequency, p. 19

- $\overline{v_n^2},\,\overline{i_n^2}$  noise mean square value, p. 12

- $\overline{v_x^2}, \overline{i_x^2}$  signal mean square value, p. 14

- $\phi_c$  carrier phase, p. 19

- $\phi_m(t)$  phase of modulating signal, p. 19

- $f_c$  noise corner frequency, p. 17

- $g_m$  small-signal transconductance, p. 15

- $h_{lpf}$  low-pass filter impulse response, p. 21

- $k_{lna}$  low noise amplifier gain, p. 21

- $k_{lpf}$  low-pass filter gain, p. 21

- m(t) modulating signal, p. 19

- n(t) noise signal, p. 21

- q elementary charge  $(1.6021766208 \times 10^{-19} C)$ , p. 16

noise voltage/current root mean square (rms) value, p. 12

signal voltage/current root mean square (rms) value, p. 14

$v_{n,rms}, i_{n,rms}$

$v_n(t), i_n(t)$  noise voltage/current (in the time domain), p. 12

$v_{x,rms}, i_{x,rms}$

k Boltzmann constant

$$(1.38064852 \times 10^{-23} \frac{J}{K})$$

, p. 14

# List of abbreviations

- AC Alternating current, p. 3

- ADC Analog-to-digital converter, p. 8

- APS Active pixel sensor, p. 2

- CAS Computer algebra system, p. 28

- CCD Charge-coupled device, p. 2

- CMOS Complementary metal-oxide semiconductor, p. 5

- CMP Chemical-mechanical polishing/planarization, p. 47

- CMRR Common-mode rejection ratio, p. 61

- DC Direct current, p. 4

- DFT Discrete Fourier transform, p. 68

- DRC Design rules check, p. 47

- DSB-FC Double side band-full carrier, p. 19

- DSB-SC Double side band-suppressed carrier, p. 19

- DSP Digital signal processor, p. 3

- EDA Electronic design automation, p. 47

- EKV Enz-Krummenacher-Vittoz model, p. 28

- FAWG Function/Arbitrary waveform generator, p. 26

- FPGA Field-programmable gate array, p. 3

- I/O Input/output, p. 55

- IC Integrated circuit, p. 29

| LAPS   | Light addressable potentiometric sensors, p. 5                     |

|--------|--------------------------------------------------------------------|

| LED    | Light-emitting diode, p. 2                                         |

| LIA    | Lock-in amplifier, p. 26                                           |

| LNA    | Low noise amplifier, p. 3                                          |

| LO     | Local oscillator, p. 26                                            |

| LPF    | Low-pass filter, p. 27                                             |

| LVS    | Layout versus schematic, p. 47                                     |

| MIM    | Metal-Insulator-Metal capacitor, p. 31                             |

| MOSFET | Metal-oxide-semiconductor field-effect transistor, p. $6$          |

| MPW    | Multi project wafer, p. 31                                         |

| NMOS   | n-channel metal-oxide-semiconductor field-effect transistor, p. 50 |

| OTA    | Operational transconductance amplifier, p. 9                       |

| PCB    | Printed circuit board, p. 76                                       |

| PDK    | Process design kit, p. 58                                          |

| PLL    | Phase-locked loop, p. 6                                            |

| PMMA   | Polymethyl methacrylate, p. 1                                      |

| PMOS   | p-channel metal-oxide-semiconductor field-effect transistor, p. 50 |

| POF    | Plastic/polymer optical fiber, p. 4                                |

| PSD    | Power spectral density, p. 12                                      |

| PSP    | Penn State Phillips MOSFET compact model, p. 58                    |

| PSRR   | Power-supply rejection ratio, p. 61                                |

| RIE    | Reactive ion etching, p. 47                                        |

| SNR    | Signal-to-noise ratio, p. 13                                       |

| THD    | Total harmonic distortion, p. 60                                   |

| TIA    | Transimpedance amplifier, p. 26                                    |

# Chapter 1

# Introduction

Fiber optic sensors comprise a technology that has recently emerged in the wake of development and increased use of optical fibers and optoelectronic components in communications and consumer goods. Based on their operation principle, or modulation and demodulation processes, one can distinguish different types of sensors, such as those based on the measurement of the amount of change in luminous intensity, polarization, phase and wavelength of the signal propagating in the fiber due to surrounding environment perturbations [1]. Different types of fibers may be used as sensor elements, such as the traditional glass fiber, and plastic fibers, which are made of polymers, such as the polymethyl methacrylate (PMMA) [2].

Due to the continuous and gradual development of the fibers and optoelectronic devices, reducing manufacturing costs and advantages over conventional electronic sensors, fiber optic sensors are being used more often every day. Among its advantages, stand out [1–3]:

- easy integration into a wide variety of structures;

- inability to conduct electric current;

- immunity to electromagnetic interference;

- reduced mass;

- robustness;

- high sensitivity;

- high bandwidth;

- multiplexing capability (to form sensor networks);

- fitness for remote sensing;

• the capacity of sensing several parameters such as refractive index, position, vibration, strain, displacement, velocity (linear and angular), temperature, humidity, viscosity, pressure, electric current, electric/magnetic field, acoustic signals, corrosion, among others.

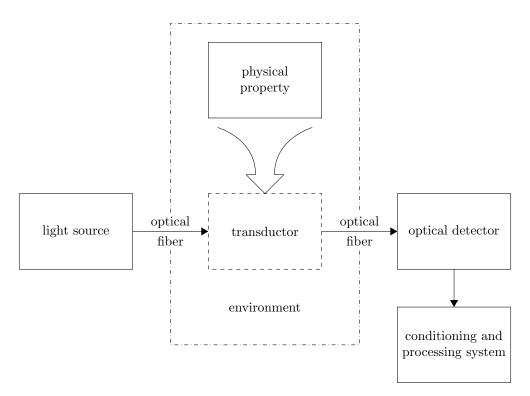

Figure 1.1: Structure of a fiber optic sensor, with a light source to generate an optical reference, an optical fiber and transductor, where the optical reference will be modulated accordingly to a physical property whose magnitude is desired, an optical detector to convert the optical signal to an electrical signal and a conditioning and processing circuit where the signal is demodulated.

The structure of a fiber optic sensor is shown in Figure 1.1. It consists of a light source (laser, LED, laser diode, etc.), optical fiber, optical detector (photodiode, APS, CCD etc.), electronic circuitry for conditioning and processing the signal generated by the detector, and in the case of an extrinsic sensor, a sensor or modulator element (the transducer), which converts a physical quantity (the measurand) into an optical signal.

In the extrinsic type of fiber optic sensor, fiber is simply used to guide the light to the sensor element and from there to the photodetector. In the case of an intrinsic fiber optic sensor, one or more physical properties of the fiber are changed. The external environment acts on the fiber disturbing the light signal that propagates inside it, thereby changing some characteristics of the signal.

## 1.1 Lock-in amplifier

A characteristic of sensors, in general, is the low amplitude of the generated signal. In certain applications, the signal amplitude gets to be of the same order of magnitude, or even lower, than the noise generated by external sources and by the own electronic circuit. Under these circumstances, the signal-to-noise ratio may display a much lower value than the unit, so that the use of traditional filtering techniques becomes impracticable.

In such situations, and when the sensor signal is an amplitude and/or phase modulated signal of known frequency, a lock-in amplifier can be used to retrieve and amplify it, improving the signal-to-noise ratio.

Commercial lock-in amplifiers are signal recovery instruments widely used in industry, especially in the measurement of chemical and physical variables. They are bulky, heavy and expensive equipment and, roughly speaking, can be seen as simple AC voltmeters. They can be analog or digital (implemented in DSP / FPGA).

Lock-in amplifiers are based on the synchronous detection principle, which is used to highlight the input signal component that has the same frequency and phase of a reference signal, and reject components at other frequencies. This technique reduces the noise bandwidth and extracts a known frequency signal, even if its amplitude is very small.

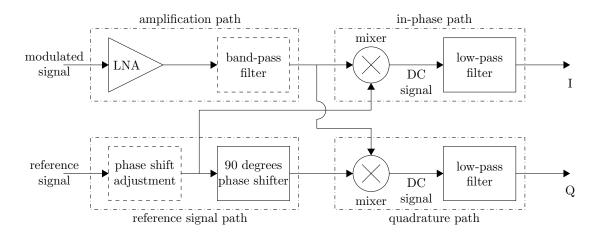

The block diagram of a two-phase analog lock-in amplifier is shown in Figure 1.2. A lock-in is said two-phase when it has two demodulators, one generating an inphase component, and the other, a quadrature component. This scheme allows for the estimation of amplitude and phase of the input signal without the need for adjusting the reference signal phase. A single-phase lock-in, on the other hand, has only one demodulator and, therefore, requires a phase adjustment circuit to recover only the amplitude of the input signal.

In the topology shown in Figure 1.2, the low noise amplifier (LNA) amplifies the modulated signal generated by the sensor element. Then, as the frequency of the modulated signal is known, a band-pass filter with a cut-off frequency equal to the signal frequency is used to conduct a "pre-filtering", to reduce the noise bandwidth and weaken external interferences. From there, the synchronous demodulation is developed. The modulated signal is multiplied by a reference signal with the same frequency and phase through the mixer, generating a rectified signal which includes a constant term proportional to the input signal level. Then, this signal is filtered to separate the constant term from the generated high order components. In this demodulation process, all noise and interferences that are not correlated with the reference, that is the common case, average to zero in the final output.

The preceding paragraph describes the working principle of an analog single-

Figure 1.2: Block diagram of an analog two-phase lock-in amplifier (optional components are enclosed in a dashed box) comprising an amplification path, two synchronous demodulators, each one consisting of the in-phase and quadrature channels, and a reference signal path that generates an appropriate reference for the demodulators.

phase lock-in amplifier. In a two-phase lock-in amplifier, a second mixer is used to demodulate the amplified signal by means of a quadrature reference signal. This procedure produces a DC signal whose average value is proportional to the phase difference between the input signal and the reference signal.

Although commercial lock-in amplifiers are widely used in instrumentation laboratories, integrated versions are not easily found for sale. One can read about them only in scientific publications, thereby hampering other applications, especially those requiring portability and low power.

## **1.2** Motivation and objectives

Taking as starting point the work published in [4], where plastic optical fiber sensors based on amplitude modulation were developed for determining the refraction index of an aqueous medium, the present work strives to propose and develop an analog lock-in amplifier for conditioning the signal generated by the photodetector (photodiode) at the end of the plastic optical fiber (POF).

The relevance of the proposed work can be atested when it is understood as a second step, aggregator and driver, in the transfer of the knowledge gained in academia to society. The first step is the initial research itself ([4]), and the proposed work encourages the transfer of academic knowledge to society by adding other insights and requirements directed to create a commercial product.

The creation of a commercial product is possible if the conditioning and signal processing systems implemented by the data acquisition board and the Matlab/Simulink software in [4], are integrated on silicon. This integration provides, among other items:

- product customization capabilities

- portability

- mass production capacity

- cost reduction of the final product

The proposed lock-in amplifier topology applies to all sensors based on amplitude modulation and having a photodiode as optical detector. This type of sensor produces a very low signal amplitude. If this signal is in an environment with many interference sources, obtaining the signal by a linear filtering operation may be infeasible. The lock-in amplifier is critical in scenarios such as this, to amplify the signal and improve the signal-to-noise ratio. Obviously, the lock-in amplifier is not limited to fiber optic sensor applications, it can be adapted to any situation where there is a need to recover a signal immersed in noise (even if the noise is much greater than the signal), or simply improve the signal-to-noise ratio.

### **1.3** Literature review

Several works on the design of analog integrated lock-in amplifiers for use in sensors exist in the literature. Amplifiers have been designed for specific purposes, such as lock-ins for Light Addressable Potentiometric Sensors (LAPS) [5]; for detecting small quantities of gas through a resistive sensor [6–10]; for optical coherence tomography signal detection [11]; for the detection of small amplitude signals in magnetically stimulated mechanical resonators [12, 13]; for hydrogen detection by a sensor based on palladium nanowire [14]; for optical sensors and spectroscopy [15, 16] and for detectors in terahertz imagers [17]. General-purpose lock-in amplifiers have also been developed [18–22]. Among these, single-phase [5–7, 15, 16, 18–21] and twophase [8–14, 17, 22] systems were designed.

All works have chosen to design their systems in a CMOS technology due to the fact that a large range of element sensor types can be integrated in this kind of technology. This opens up the possibility to create a monolithic sensor system, which consists of the sensing element and conditioning and signal processing circuits, all integrated on a single die. Furthermore, the CMOS manufacturing process of components is well known and already established in the industry. Compared with other technologies, this provides the manufacture of reliable components at a low cost. Some researches persist for long periods and present, in several articles, the results obtained during different moments. One of these researches began with [5], which had shown a lock-in amplifier manufactured in a 0.6  $\mu$ m technology, and has evolved by adapting the initial topology and changing certain characteristics such as gain and operating frequency. Thus, discrete prototypes were presented in [6, 8, 9] and integrated ones in [7, 10] to validate the various proposed changes. Other studies published in early articles present just the simulation results and later, in other articles, the experimental results, as in [12, 13] and [19–21]. The work presented in [16] was based on the system topology presented in [15] and was limited to modify the topology of certain blocks, only presenting simulation results.

Most of the studies present systems whose purpose is to condition voltage signals, and just a few are designed to condition current signals [11, 14–16].

In [18], an analog lock-in amplifier with a topology similar to the one in Figure 1.2 was fabricated in a 0.7  $\mu$ m CMOS technology. An instrumentation amplifier receives the sensor signal that is again amplified and filtered by a MOSFET-C bandpass amplifier with adjustable gain. The bandpass characteristic of the amplifier reduces the noise bandwidth and the influence of external interferences. The mixer, also implemented in a MOSFET-C technique, receives the sinusoidal reference signal generated by a PLL, as in commercial equipment, which generates the reference signal locally from an external clock. To eliminate the high frequency components of the rectified signal generated by the mixer, a low-pass switched-capacitor filter is used, with a variable cutoff frequency through the adjustment of the switching frequency and three control bits. All blocks have differential inputs and outputs. To convert the differential signal output in a single-ended signal, a DC amplifier with offset adjustment is used.

The lock-in amplifier presented in [5] bears similarities with the previous work. Its gain stage also has an instrumentation amplifier at the input, followed by a bandpass  $G_m$ -C filter with a selection bit for selecting the filter cut-off frequency (1 or 10 KHz), and by a programmable gain amplifier. The demodulator is implemented by a switched unitary gain amplifier, that alters the gain from positive to negative when the amplitude of the input sine wave turns to be negative. The reference channel receives an external clock and has a circuit for phase adjustment and another that generates a ninety degree phase shift in the clock, to allow the adjustment of the output of the lock-in amplifier (the output must provide zero volts). After adjustment, the phase shift circuit is inhibited and the reference signal has now the same phase as the signal in the gain path. A low-pass second order  $G_m$ -C filter follows the mixer.

The work presented in [6] is a continuation of [5]. Regarding the system topology, the amplifier at the output of the gain stage was eliminated. Moreover, the internal topology of the differential amplifiers, that serve as basic building blocks for the instrumentation amplifier and the mixer, has changed. The operating frequency range of the lock-in amplifier has also changed. Now, the system can work with frequency values of 11 Hz, 17 Hz, and 77 Hz. Three second-order active band-pass filters, each one with a cutoff frequency set for each one of the three frequencies, have been implemented. To cope with such low frequencies for the input signal, the low-pass filter was changed to a fourth-order cascade Gm-C filter with 1.3 mHz cutoff frequency. A discrete prototype that operates at a frequency of 77 Hz was developed and validated.

The above system is again modified in [7]. In this work, the band-pass filter was eliminated from the system and the topology of the amplifiers was changed one more time. The phase adjustment circuit was also modified. In this, as well as in the two previous works, the resistor of the instrumentation amplifier that allows the adjustment of the gain is implemented as a discrete component, external to the integrated circuit, just to allow the adjustment of the gain by changing the resistor. The low-pass filter was changed again. Now, it is implemented by a discrete cascade of four RC cells, with a cutoff frequency of 100 mHz.

In [8, 9] the topology of the previous work changed significantly. The lock-in amplifier has now a topology with several blocks to implement an automatic phase adjustment. The band-pass filter returns to the input path, and the system starts now to feed back the phase adjustment circuit and the ninety degree phase lag block with the system output signals, representing the error in the detection of the amplitude of the input signal and the error in the detection of phase, respectively. The system was again implemented with discrete elements and validated, showing excellent results.

The previous work is complemented by [10], which adds the automatic adjustment capacity of the frequency of the reference signal. An integrated version of the system is presented and the excellent results shown by the discrete prototype are ratified.

In [11], a two-phase lock-in amplifier is designed and manufactured for signal detection in optical coherence tomography systems, with an interferogram signal that has a carrier frequency of 100 kHz and a bandwidth of 5 kHz. The designed system consists of a transimpedance amplifier with differential output, for converting the current signal from the optical detector into a voltage signal. This block is not considered by the authors as pertaining to the lock-in amplifier architecture. The transimpedance amplifier has adjustable gain and rejection capability. A differential gain stage, with differential input and output, amplifies the signal generated by the transimpedance amplifier and feeds the demodulators. These are based on the Gilbert cell and have a differential input and a single-terminated output. Finally,

each demodulator is followed by a third-order Butterworth switched-capacitor filter with a designed cutoff frequency of 5 kHz and adjustable by means of the clock. The clock is generated by a voltage controlled oscillator based on Schmitt triggers. The reference signal is generated externally. The fabricated circuit was validated in the application for which it was designed and demonstrated efficiency.

A lock-in amplifier is developed aiming at magnetically stimulated mechanical resonator applications. Simulation results are presented in [12], while their experimental results are provided in [13]. The system has, in its input signal amplification path, an instrumentation amplifier, followed by a differential second-order  $G_m$ -C high-pass filter with external capacitors to allow its adjustment, and a programmable gain stage. The demodulators are implemented through passive N-MOS bridges, and the low-pass filters through second-order passive networks with discrete capacitors, as in the high-pass filter. In this project, the lock-in amplifier is accompanied by a fixed gain amplifier with offset adjustment, a programmable gain amplifier and a  $\Delta\Sigma$  analog-to-digital converter (ADC). The reference signal (square) is generated externally. This signal also serves as a reference for a PLL, external to the designed system, that will generate the necessary signal to stimulate the sensor.

In [14] a two-phase lock-in amplifier is designed to detect the signal of the current flowing through a palladium nanowire when stimulated by a sinusoidal signal voltage. To this end, it presents in its amplification path a current-voltage converter at its entrance, followed by a second-order switched-capacitor band-pass filter. The demodulators have a particular topology, consisting of a thermometric code generator, followed by control switches and an analog adder. The second-order switchedcapacitor low-pass filters provide a DC signal at the output of the in-phase and quadrature signal paths which represent, respectively, a value proportional to the amplitude of the current signal (or voltage) generated by the nanowire and a value proportional to the amount of phase error between the reference signal and the input signal voltage.

In [15], the authors developed a lock-in amplifier for optic applications and spectroscopy with operating frequency range from 13 to 25 kHz. The system topology is similar to the one presented in [14] and the differences are in the fact that the amplifier developed in [14] has a two-phase topology, while the one developed in [15] has a single-phase topology. Moreover, high-pass filters follow the transimpedance amplifier and the band-pass filter in order to eliminate the DC component of the signal generated by both blocks. In this paper, also, the signal of the amplifying path, after being amplified, is used as a reference for a PLL, which will generate the local reference signal having the same phase and frequency of the signal generated by the sensor. The filters are all second-order  $G_m$ -C and the mixer is based on a Gilbert cell. In the PLL, the voltage controlled oscillator is based on a ring oscillator and the second-order loop filter is composed of discrete components, external to the integrated circuit.

The same authors developed in [22] an integrated lock-in amplifier for operating frequencies ranging between 15 and 20 MHz. The introduced topology is quite different from the traditional one, becoming a mixed-signal system with analog and digital blocks. The designed system was able to track the input signal amplitude and phase.

In [19–21] an analog integrated single-phase lock-in amplifier, for applications that require portability, was developed using an unconventional strategy. The volt-age signal from the sensor element is converted into a current signal by means of a transcondutor, and synchronous demodulation is performed by a mixer that operates in current mode. A current splitter block provides gain adjustment capability through three bits. Finally, the current signal is converted into a voltage one by a transimpedance amplifier and the converted signal is filtered by a passive discrete RC filter (external to the integrated circuit), with a 5 Hz cutoff frequency.

The manufactured system was characterized and used in a practical test where the objective was to detect a small concentration of carbon monoxide mixed with a mass of nitrogen. Compared to other studies, the lock-in amplifier showed excellent electrical characteristics, despite not having integrated the output low-pass filter, nor the OTA bandwidth adjustment capacitors. There was no circuit for generating an internal reference signal to the demodulator. The reference signals were generated externally, by bench function generators. In the practical experiment, the designed lock-in amplifier was able to detect carbon monoxide concentrations in the order of units of ppms.

A lock-in amplifier was designed and presented in [17] to condition signals from terahertz detectors. The long-term goal of the project is to integrate the circuit along with terahertz imagers. The system comprises a low noise amplifier followed by four mixers, each one receiving the amplified signal and the reference signal lagged by, respectively,  $0^{\circ}$ ,  $90^{\circ}$ ,  $180^{\circ}$  and  $270^{\circ}$ . The delayed signals are generated by a specific circuit, driven by an external clock. The DC signal at the output of demodulators that receive the reference signals lagged  $0^{\circ}$  and  $180^{\circ}$ , feed a differential amplifier, whose goal is to eliminate the offset of the previous blocks. The signal generated by this differential amplifier is said in-phase and passes through a low-pass filter to eliminate high-frequency signal components and obtain a DC value proportional to the amplitude of the input signal. For the generation of the quadrature signal, proportional to the phase difference between the input signal and the reference signal, the same scheme is applied, using for this purpose the DC signal at the output of the other two demodulators.

# Chapter 2

## System Level Analysis

Lock-in systems are signal recovery instruments that are generally used to carry out measurements in situations where signals of interest are overshadowed by noise and interferences.

There are several techniques for signal recovery, such as the ones based on linear filtering operations, waveform averaging and signal correlation. But, the one that proved most successful was that based on the synchronous detection principle, the lock-in amplifier.

A synchronous detector measures variations in a signal of interest by using a synchronous reference, that can be derived from the input modulator. It shall be find that detection with respect to a synchronous reference enables the use of very long averaging times for the purpose of signal-to-noise ratio (SNR) improvement and that practical systems are capable of operating with signals well below the background noise level.

Synchronous detectors offer a significant advance over alternative amplitudedemodulation schemes employing non-linear devices such as envelope detectors. The latter make no fundamental distinction between signal and noise components, whereas a synchronous detector is engineered to respond specifically to the information-bearing signal.

A synchronous detector is responsive to the amplitude of a signal but is also sensitive to the phase difference between a signal and the reference. Therefore, it can be devised to measure variations in both the amplitude and phase of periodic signals in the presence of noise and interference.

A lock-in system is that one operating on the synchronous detector principle and a lock-in amplifier is a lock-in system that encompasses a synchronous detector, preamplifiers and a reference processing circuit.

In general, applications can be divided into two main categories: the one where lock-in systems are used in their long-established role as signal-recovery tools for the measurement of modulated signal in noise; and the other, where lock-in systems are used for the precision measurement of signals, in situations where signal-recovery capability does not appear to be a prime consideration. The application aimed by this work is better classified in the second category. Appendix 1 of [23] presents an almost exhaustive list of areas where lock-in amplifiers can be employed.

In the case of an optic fiber sensor, considering that the process is essentially linear, that is, no new frequencies are generated between input and output, the signal of interest appears in the output of the transducer with the same frequency as the fundamental excitation frequency.

The measurement of the phase-shift introduced by the experiment might be of interest, but, very often, it is sufficient to only monitor changes in the magnitude of the output signal.

In the envisaged application, the objective is to determine the concentration of bacteria in water through the measurement of refractive index of the liquid by a plastic optical fiber (POF) sensor. The modulated signal output by the transducer (photodiode) conveys a modulating signal that is slowly varying, not just with respect to the excitation frequency, but also with respect to observation interval. Indeed, in many circumstances the signal may have fixed characteristics throughout the time available for measurement.

In this chapter, some important concepts on signals and noise in the time and frequency domains are briefly revised, the basic theory that underlies the lock-in amplifier operation is introduced, the proposed lock-in amplifier system level architecture is presented and, finally, comments about the employed circuit sizing methodology are made.

## 2.1 Considerations on signals and noise

A distinction between interference sources of external origin and noise, which is inherent to the measurement system, is usually made. Interference occurs if the received energy transferred through an unintended coupling path causes the circuit to behave in an undesired manner, provided the received energy is of sufficient magnitude and/or spectral content. The means to mitigate external interferences are: (1) suppress the emission at its source; (2) make the coupling path as inefficient as possible; and (3) make the circuit less susceptible to coupled energy [24]. In its turn, the intrinsic circuit noise is analyzed and worked during design.

### 2.1.1 Noise

#### Time domain

As noise is a random process, the instantaneous value of noise in the time domain cannot be predicted at any time even if the past values are known. So, to take into account noise on system modeling, it is usual to use the noise mean square value, sometimes referred as average normalized noise power, according to Equations 2.1 and 2.2, or its root mean square value, according to Equations 2.3 and 2.4, as a statistical model for the noise [25, 26],

$$\overline{v_n^2} = \lim_{T_p \to +\infty} \frac{1}{T_p} \int_0^{T_p} v_n^2(t) \, dt \qquad [V^2]$$

(2.1)

$$\overline{i_n^2} = \lim_{T_p \to +\infty} \frac{1}{T_p} \int_0^{T_p} i_n^2(t) \, dt \qquad [A^2]$$

(2.2)

$$v_{n,rms} = \sqrt{\lim_{T_p \to +\infty} \frac{1}{T_p} \int_0^{T_p} v_n^2(t) \, dt} \qquad [V]$$

(2.3)

$$i_{n,rms} = \sqrt{\lim_{T_p \to +\infty} \frac{1}{T_p} \int_0^{T_p} i_n^2(t) \, dt} \qquad [A]$$

(2.4)

where  $v_n$  is a noise voltage and  $i_n$  a noise current.

Knowing the noise mean square value, one can readily calculate the actual power delivered to a load  $R_L$  as  $\frac{\overline{v_n^2}}{R_L}$  or  $\overline{i_n^2}R_L$ .

#### **Frequency domain**

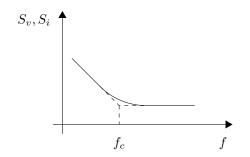

In practice, noise power measurements are used in systems with well-defined impedance levels. Elsewhere, it is generally more convenient to use the concept of power spectral density (PSD) of the noise signal. The PSD shows the power the signal carries at each frequency. More specifically, it is defined as the average power carried by a noise signal in a 1 Hertz bandwidth around a frequency f. The PSD is expressed in units of  $\frac{V^2}{Hz}$  and  $\frac{A^2}{Hz}$ . An example of the typical characteristic of the PSD of a signal is shown in Figure 2.1.

The noise corner frequency  $f_c$  delimits two regions in the plot. At low frequencies, the noise is dominated by flicker noise, whereas at higher frequencies, broadband noise dominates.

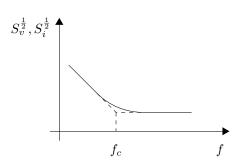

It is also common to work with the square root of the noise power spectral density.

Figure 2.1: Example of the PSD of a voltage  $(S_v(f))$  and current  $(S_i(f))$  signals, showing the dominance of flicker noise at frequencies below the corner frequency  $f_c$ , and the dominance of thermal noise at frequencies above  $f_c$ .

This value is termed the amplitude spectral density, or root spectral density, and is expressed in units of  $\frac{V}{\sqrt{Hz}}$  and  $\frac{A}{\sqrt{Hz}}$ , as shown in Figure 2.2.

Figure 2.2: Example of the amplitude spectral density of a voltage  $(S_v^{\frac{1}{2}}(f))$  and current  $(S_i^{\frac{1}{2}}(f))$  signals demonstrating the dominance of flicker noise at frequencies below the corner frequency  $f_c$ , and the dominance of thermal noise at frequencies above  $f_c$ .

The root mean square value of the noise signal can also be obtained in the frequency domain by

$$v_{n,rms} = \sqrt{\int_0^{+\infty} S_v(f) \, df} \qquad [V]$$

(2.5)

$$i_{n,rms} = \sqrt{\int_0^{+\infty} S_i(f) \, df} \qquad [A]$$

(2.6)

In practice, the root mean square noise within a specified frequency range can be computed by taking the extremes of the frequency interval as integration limits.

### 2.1.2 Signal-to-noise ratio

Knowing how to obtain the mean square value of noise, the signal-to-noise ratio (SNR) of a node in a system can be now defined as [26]

$$SNR = \frac{\text{signal power}}{\text{noise power}}$$

(2.7)

or in decibels (dB) as

$$SNR = 10 \log\left(\frac{\overline{v_x^2}}{\overline{v_n^2}}\right) = 20 \log\left(\frac{v_{x,rms}}{v_{n,rms}}\right) \qquad [dB]$$

(2.8)

$$SNR = 10 \log\left(\frac{\overline{i_x^2}}{\overline{i_n^2}}\right) = 20 \log\left(\frac{i_{x,rms}}{i_{n,rms}}\right) \qquad [dB]$$

(2.9)

where  $\overline{v_x^2}$  and  $\overline{i_x^2}$  are the signal mean square values and  $v_{x,rms}$  and  $i_{x,rms}$  the root mean square values.

### 2.1.3 Broadband noise

Broadband noise (or white noise) is known to have a constant power spectral density over all the frequency spectrum or, in practice, over the frequency range of interest.

#### Thermal noise

In semiconductors, a major source of noise is thermal noise (also known as Johnson noise or Nyquist noise). It is generated by the random motion of electrons in a resistive material and in a temperature other than the absolute zero.

For a resistor, the thermal noise can be modelled by a voltage source  $S_{v,th}$  with a convenient arbitrated polarity in series with the noiseless resistor, or by a current source  $S_{i,th}$  in parallel with the noiseless resistor, as shown in Figure 2.3. The one-sided power spectral density<sup>1</sup> is found to be given by

$$S_{v,th} = 4kTR \qquad \left[\frac{V^2}{Hz}\right] \tag{2.10}$$

$$S_{i,th} = \frac{4kT}{R} \qquad \left[\frac{A^2}{Hz}\right] \tag{2.11}$$

where  $k = 1.38064852 \times 10^{-23}$  J/K is the Boltzmann constant, T the temperature in Kelvins and R the resistance value. For the models to hold equivalence,  $\frac{S_{v,th}}{R^2} = S_{i,th}$ . For a MOSFET, the modeling of thermal noise is a tough matter as the noise varies with the operating region of the transistor, and an all-region equation invari-

<sup>&</sup>lt;sup>1</sup>In the one-sided spectral density, f is constrained to the interval  $[0; +\infty[$ , while in the two-sided spectral density, f is constrained to the interval  $]-\infty; +\infty[$ .

Figure 2.3: Models for a noisy resistor.

ably results in a complex expression. But, for the common case of a long-channel device operating in strong inversion and in saturation, it is generally accepted to model the noise generated in the channel of the MOSFET by a current source connected between the drain and source terminals (shown in Figure 2.4) with a power spectral density [26]

$$S_{i,th} = 4kT\gamma g_m \qquad \left[\frac{A^2}{Hz}\right]$$

(2.12)

where  $g_m$  is the device small-signal transconductance, and the white noise parameter  $\gamma$  is assumed to be equal to  $\frac{2}{3}$  for a long-channel transistor and may need to be replaced by a larger value for submicron devices.

Figure 2.4: Model of a noisy (a) nmos transistor; (b) pmos transistor.

#### Shot noise

Shot noise is associated with a DC flow produced by carriers crossing a potential barrier and is attributed to the passage of discrete charge carriers. Carriers can cross the barrier provided they have sufficient energy to do so; some carriers cross, and some do not. The large numbers of carriers that do cross, each carrying a charge of magnitude q, generates an average current  $I_{DC}$ . On top of this is superimposed a minute fluctuation due to the randomness in the flow of individual charge carriers over the barrier. For this reason, shot noise have a power spectral density [27]

$$S_{i,sh} = 2qI_{DC} \qquad \left[\frac{A^2}{Hz}\right] \tag{2.13}$$

where q is the elementary charge  $(1.6021766208 \times 10^{-19} C)$  and  $I_{DC}$ , as mentioned before, is the average current.

Shot noise will be present in all semiconductor devices operating with finite bias current, and is usually the dominant source of broadband noise in optical detectors [23]. Here, a periodic current variation due to a variable intensity light beam must often be measured against a more or less steady bias current which flows in response to a much greater "background" illumination due to light leakage. Many such detectors conform closely to an ideal current source, and the output can be measured by connecting the detector to an external load resistor  $R_L$ . Figure 2.5 gives the noise equivalent circuit of this arrangement, which shows that the signal current  $i_s$ appears in competition with the shot noise current  $i_{sh}$  of the bias current  $I_{DC}$  and the thermal noise current  $i_{th}$  of the load resistor.

Figure 2.5: Noise equivalent circuit of an optical detector and its various components:  $i_s$  - signal current,  $I_{DC}$  - bias current,  $i_{sh}$  - shot noise current and  $i_{th}$  - thermal noise current.

To ensure that the signal-to-noise ratio inherent to the detector is not degraded further by the thermal noise in  $R_L$ , the following condition can be investigated:

$$2qI_{DC} \geqslant \frac{4kT}{R_L} \tag{2.14}$$

which gives

$$R_L \geqslant \frac{2kT}{qI_{DC}} \tag{2.15}$$

### 2.1.4 Low-frequency noise

#### Flicker noise

A significant type of low-frequency noise is flicker noise, also known as  $\frac{1}{f}$  noise or pink noise, that with thermal noise constitute the two types of dominant noise in MOSFETs. Flicker noise is attributed primarily to: (1) the trapping and releasing of charge carriers that move near the gate oxide and silicon substrate interface, due to extra energy states that exist in this interface; (2) to mobility fluctuations, due to lattice scattering [27].

The flicker noise is usually modelled by a voltage source in series with the gate with power spectral density given by

$$S_{v,fl} = \frac{K}{C'_{ox}WLf} \qquad \left[\frac{V^2}{Hz}\right] \tag{2.16}$$

where K is a process-dependent constant,  $C_{ox}$  is the gate-oxide capacitance per unit area, W and L are, respectively, the transistor channel width and length, and f is the operating frequency.

When both, flicker noise and thermal noise are ploted in the same graph, the flicker noise corner  $(f_c)$  can be perceived in the intersection between the curves (refer to Figures 2.1 and 2.2). This point can be roughly determined by equaling the noises after transforming the gate noise source in an equivalent channel current source, as [25]

$$4kT\left(\frac{2}{3}\right)g_m = \frac{K}{C'_{ox}WLf_c}g_m^2 \tag{2.17}$$

that is,

$$f_c = \frac{3Kg_m}{8kTC'_{ox}WL} \qquad [Hz] \tag{2.18}$$

### 2.2 Filtered noise and noise bandwidth

The bandwidth of the noise that appears together with the signal at the output of the transducer, is always fixed at a well defined value due to the low-pass filter effect caused by the capacitance of the transducer and the input resistance of the circuit that follows, generally a high input impedance LNA.

If the low-pass characteristic of the transducer/LNA combination can be expressed by a transfer function  $H(j\omega)$ , the output spectral density of the noise is expressed by

$$S_{v,out} = S_{v,in} |H(j\omega)|^2 \qquad \left[\frac{V^2}{Hz}\right]$$

(2.19)

$$S_{i,out} = S_{i,in} |H(j\omega)|^2 \qquad \left[\frac{A^2}{Hz}\right]$$

(2.20)

The root spectral densities can be obtained by taking the square root of both sides in 2.19 and 2.20.

$$S_{v,out}^{\frac{1}{2}} = S_{v,in}^{\frac{1}{2}} |H(j\omega)| \qquad \left[\frac{V}{\sqrt{Hz}}\right]$$

(2.21)

$$S_{i,out}^{\frac{1}{2}} = S_{i,in}^{\frac{1}{2}} |H\left(j\omega\right)| \qquad \left[\frac{A}{\sqrt{Hz}}\right]$$

(2.22)

To calculate the total output mean square value, Equations 2.19 and 2.20 are integrated over the entire spectrum, that is,

$$\overline{v_n^2} = \int_0^{+\infty} S_{v,in} |H(j\omega)|^2 df \qquad [V^2]$$

(2.23)

$$\overline{i_n^2} = \int_0^{+\infty} S_{i,in} |H(j\omega)|^2 df \qquad [A^2]$$

(2.24)

As previously mentioned, the average power spectral density is determined by the noise power within a 1-Hz bandwidth. This 1-Hz bandwidth is thought of as an ideal band-pass filter with a gain of 1 and a steep characteristic. However, practical filters have a more smooth characteristic. To account for this fact, the noise equivalent bandwidth  $BW_n$  (or, simply, noise bandwidth) of a given filter is defined as the bandwidth of an ideal filter that has the same RMS output noise as that of the given filters. In other words, given a filter frequency response with peak gain  $A_0$ , the noise bandwidth is the width of the ideal filter that has the same area and gain,  $A_0$ , as that of the original filter (Figure 2.6).

Figure 2.6: Noise bandwidth  $BW_n$  and its comparison to the bandwidth of a practical filter.

The advantage of knowing the noise bandwidth of a filter is that when white noise is applied to the filter input, the total output noise mean square value is easily calculated by multiplying the average power spectral density by the noise bandwidth as

$$\overline{v_n^2} = S_{v,out} B W_n \, df \qquad \left[ V^2 \right] \tag{2.25}$$

$$\overline{i_n^2} = S_{i,out} B W_n \, df \qquad \left[A^2\right] \tag{2.26}$$

## 2.3 Signal spectrum and modulation

In lock-in measurements, the signal is usually amplitude- and/or phase-modulated, and therefore a previous knowledge of at least the sketch of the signal is necessary.

Considering a carrier wave

$$c(t) = A_c \cos\left(\omega_c t + \phi_c\right) \tag{2.27}$$

where  $A_c$  is the carrier amplitude,  $\omega_c$  the carrier frequency and  $\phi_c$  the carrier phase with respect to an arbitrated reference, an amplitude-modulated signal is described by:

$$s_{am}(t) = [1 + m(t)] c(t)$$

=  $A_c [1 + m(t)] \cos(\omega_c t + \phi_c)$  (2.28)

=  $A_c \cos(\omega_c t + \phi_c) + A_c m(t) \cos(\omega_c t + \phi_c)$

while a phase-modulated signal is given by:

$$s_{pm}(t) = A_c \cos \left[\omega_c t + m(t)\right]$$

=  $A_c \left[\cos \left(\omega_c t\right) \cos \left(m(t)\right) - \sin \left(\omega_c t\right) \sin \left(m(t)\right)\right]$  (2.29)

where m(t) is the modulating signal that should be retrieved.

More precisely, Equation 2.28 represents the double side band-full carrier (DSB-FC) method, where the pure carrier signal is summed to the modulated signal. This is in contrast with the double side band-suppressed carrier (DSB-SC) method, where the carrier is suppressed from the modulated signal.

It is assumed that m(t) has a smaller changing rate than  $\cos(\omega_c t)$ . Indeed, the modulating signal can be very slowly varying, often having a bandwidth in the order of a few Hertz, that is, an extremely narrowband signal.

Yet, a signal modulated both in amplitude and phase (mixed modulation) is represented by:

$$s_{mm}(t) = A_c [1 + A_m(t)] \cos [\omega_c t + \phi_m(t)]$$

(2.30)

where  $A_m(t)$  and  $\phi_m(t)$  are, respectively, the amplitude and phase of modulating signal.

It is generally easier to study the signals in the frequency domain. For such end one can resort to Fourier series and transforms as well to trigonometric identities to operate with the well-defined sinusoidal carriers.

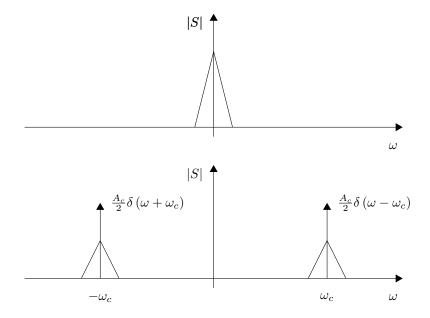

To obtain the signal spectrum of the amplitude modulated signal (e.g. Fig-

ure 2.7), the Fourier transform is applied:

$$\mathscr{F}\left\{s\left(t\right)\right\} = S\left(j\omega\right)$$

$$= \frac{A_{c}}{2}\delta\left(\omega - \omega_{c}\right) + \frac{A_{c}}{2}\delta\left(\omega + \omega_{c}\right) + \frac{A_{c}}{2}M\left(j\omega + j\omega_{c}\right) + \frac{A_{c}}{2}M\left(j\omega - j\omega_{c}\right)$$

(2.31)

The spectrum generally provides sufficient knowledge about the bandwidth of the

Figure 2.7: Spectrum magnitude of signal m(t) (above) and the spectrum of the same signal modulated by a sinusoidal carrier of frequency  $\omega_0$  and amplitude  $A_c$  (below).

modulating signal and its location along all the frequency spectrum.

In regard to phase modulation, for low-index modulation, that is, when the phase shift is very small  $(|\sin(t)| \ll 1)$ , the phase modulated signal can be approximated by:

$$s_{pm}(t) \cong A_c \left[ \cos(\omega_c t) - m(t) \sin(\omega_c t) \right]$$

$$\cong A_c \cos(\omega_c t) - A_c m(t) \sin(\omega_c t)$$

(2.32)

The above expression indicates that for small values of phase shift, the resulting phase modulation amplitude spectrum is identical to that of amplitude modulation.

#### 2.4 Fundamentals of lock-in systems

For the lock-in system depicted in Figure 1.2, its operation can be modeled by considering an amplitude modulated signal with added noise at its input,

$$s_{am}(t) = A_c [1 + m(t)] \cos(\omega_c t + \phi_c) + n(t).$$

(2.33)

At the output of the LNA, the signal finds itself amplified by a gain factor  $k_{lna}$ , as shown in

$$s'_{am}(t) = k_{lna} \left\{ A_c \left[ 1 + m(t) \right] \cos(\omega_c t + \phi_c) + n(t) \right\}.$$

(2.34)

The synchronous demodulation starts by multiplying the amplified signal by a reference, that can be the own excitation signal. The mixer response in the in-phase channel is given by

$$s_{am,i}''(t) = s_{am}'(t) r_i(t)$$

=  $k_{lna} \{A_c [1 + m(t)] \cos(\omega_c t + \phi_c) + n(t)\} A_r \cos(\omega_r t + \phi_r)$