### INTEGRATED CIRCUIT DESIGN OF A REACTIVE POWER MEASUREMENT SYSTEM USING A SWITCHED-CURRENT HILBERT TRANSFORMER

Eduardo Vilela Pinto dos Anjos

Dissertação de Mestrado apresentada ao Programa de Pós-graduação em Engenharia Elétrica, COPPE, da Universidade Federal do Rio de Janeiro, como parte dos requisitos necessários à obtenção do título de Mestre em Engenharia Elétrica.

Orientador: Fernando Antônio Pinto Barúqui

Rio de Janeiro Abril de 2016

### INTEGRATED CIRCUIT DESIGN OF A REACTIVE POWER MEASUREMENT SYSTEM USING A SWITCHED-CURRENT HILBERT TRANSFORMER

Eduardo Vilela Pinto dos Anjos

DISSERTAÇÃO SUBMETIDA AO CORPO DOCENTE DO INSTITUTO ALBERTO LUIZ COIMBRA DE PÓS-GRADUAÇÃO E PESQUISA DE ENGENHARIA (COPPE) DA UNIVERSIDADE FEDERAL DO RIO DE JANEIRO COMO PARTE DOS REQUISITOS NECESSÁRIOS PARA A OBTENÇÃO DO GRAU DE MESTRE EM CIÊNCIAS EM ENGENHARIA ELÉTRICA.

Examinada por:

Prof. Fernando Antônio Pinto Barúqui, D.Sc.

Prof. Antônio Carlos Moreirão de Queiroz, D.Sc.

Prof. Marcio Nogueira de Souza, D.Sc.

RIO DE JANEIRO, RJ – BRASIL ABRIL DE 2016 Anjos, Eduardo Vilela Pinto dos

Integrated Circuit Design of a Reactive Power Measurement System using a Switched-Current Hilbert Transformer/Eduardo Vilela Pinto dos Anjos. – Rio de Janeiro: UFRJ/COPPE, 2016.

XIX, 173 p.: il.; 29,7cm.

Orientador: Fernando Antônio Pinto Barúqui

Dissertação (mestrado) – UFRJ/COPPE/Programa de Engenharia Elétrica, 2016.

Referências Bibliográficas: p. 128 – 135.

Reactive Power Measurement.

Switched-Current.

Hilbert Transformer.

Current Memory Cell.

Barúqui, Fernando Antônio Pinto.

Universidade Federal do Rio de Janeiro, COPPE, Programa de Engenharia Elétrica.

Título.

Aos meus avós Reynaldo e Violeta.

# Agradecimentos

Primeiramente, gostaria de agradecer a minha mãe, Maria Verônica Vilela Pinto, por todo o carinho e suporte que me foi dado durante esta nova empreitada. Agradeço todo o carinho que recebi durante toda minha vida e a liberdade para traçar meu próprio futuro. Você é a grande responsável pelo engenheiro e pelo ser humano que me formei. Sem você, nada disso seria possível.

Ao meu professor e orientador, Fernando Antônio Pinto Barúqui, por toda a ajuda e direcionamento durante este projeto de pesquisa. Desafios foram enfrentados e vencidos graças ao seu apoio e disposição. Muito obrigado pela consideração e pelas oportunidades conseguidas.

To Kanako Matsuyama, my amazing love and partner. Thank you for your support, patience and advices. No matter how far you can be, you always make me feel close to you. Your support makes me stronger and makes me push myself further.

Ao meu pai, Jackson Gonçalves dos Anjos, por sua amizade e por seus conselhos e palavras de sabedoria, que levarei por toda minha vida.

Ao meu irmão Henrique Vilela Pinto dos Anjos, por sua amizade e parceria em vários momentos especiais da minha vida.

Gostaria de agradecer também aos professores Antônio Carlos Moreirão de Queiroz e Marcio Nogueira de Souza por terem aceitado participar da banca de defesa desta dissertação.

Aos membros do laboratório PADS, professores e alunos, em especial ao João Alberto de França Ferreira e Allan Bides de Andrade, pela caminhada conjunta em direção ao título de mestre.

E finalmente aos muitos amigos que compartilho meu dia-a-dia e fazer desta vida muito mais alegre e divertida, cujos nomes são muitos e faltaria espaço para tantos. Vocês sabem quem são. Resumo da Dissertação apresentada à COPPE/UFRJ como parte dos requisitos necessários para a obtenção do grau de Mestre em Ciências (M.Sc.)

### SISTEMA DE MEDIDA DE POTÊNCIA REATIVA UTILIZANDO UM TRANSFORMADOR DE HILBERT EM CORRENTE CHAVEADA INTEGRADO NA TECNOLOGIA CMOS

Eduardo Vilela Pinto dos Anjos

Abril/2016

#### Orientador: Fernando Antônio Pinto Barúqui

Programa: Engenharia Elétrica

Sistemas de Medida de Potência Reativa são uma parte fundamental dos medidores de energia modernos, e com a crescente demanda por fontes de energia renovável e geração distribuida, a procura por sistemas de medida sob condições não-senoidais aumentou na última decada. Porém, soluções em domínio analógico representam uma possibilidade de implemetação de baixo custo e não foram exploradas por trabalhos anteriores. Nesta dissertação, a teoria da medida de potência reativa é apresentada e um sistema de medida de potência reativa em domínio analógico é desenvolvido. A técnica de medida proposta emprega um transformador de Hilbert em corrente chaveada que utiliza sessões de passa-tudo estruturais para obter baixa sensibilidade ao descasamento de transistores. Para avaliar a estrutura proposta, um circuito integrado é projetado baseado em padrões internacionais estabelecidos pela Comissão Eletrotécnica Internacional (IEC). A implemetação final é testada a partir de simulação de circuitos utilizando ferramentas de *software* do estado da arte e simulações de Monte Carlo são executadas para observar a sensibilidade da medida ao descasamento de transistores. Abstract of Dissertation presented to COPPE/UFRJ as a partial fulfillment of the requirements for the degree of Master of Science (M.Sc.)

### INTEGRATED CIRCUIT DESIGN OF A REACTIVE POWER MEASUREMENT SYSTEM USING A SWITCHED-CURRENT HILBERT TRANSFORMER

Eduardo Vilela Pinto dos Anjos

April/2016

Advisor: Fernando Antônio Pinto Barúqui

Department: Electrical Engineering

Reactive Power Measurement Systems (RPMS) are a fundamental part of modern smart meters, and with the increasing demand for renewable sources and distributed generation, the search for measurement systems under non-sinusoidal conditions grew in the last decade. However, analog domain solutions were not explored by previous works and it represents a possibility for a low-cost implementation. In this thesis, the theory of reactive power measurement is studied and an analog domain RPMS is developed. The proposed measurement technique employs a switched-current Hilbert transformer that uses structurally all-pass section to achieve low-sensitivity to transistor mismatch. To evaluate the proposed structure, an integrated circuit is designed based on international standards from the International Electrotechnical Commission (IEC). The final implementation is evaluated through circuit simulation using state-of-the-art software tools and Monte Carlo simulations are performed to observe measurement sensitivity to transistor mismatch.

# Contents

| Lis      | st of | Figures   x                                               | ii       |

|----------|-------|-----------------------------------------------------------|----------|

| Lis      | st of | Tables xi                                                 | ix       |

| 1        | Intr  | oduction                                                  | 1        |

|          | 1.1   | Switched-Current Circuits                                 | 2        |

|          | 1.2   | Work Outline and Contributions                            | 4        |

| <b>2</b> | The   | Hilbert Transformer                                       | <b>5</b> |

|          | 2.1   | Hilbert Transform                                         | 5        |

|          | 2.2   | Discrete-Time Hilbert Transformer                         | 6        |

|          |       | 2.2.1 Phase Imbalance and Bandwidth                       | 9        |

|          | 2.3   | Structurally All-Pass Filters                             | 10       |

|          |       | 2.3.1 Switched-Current Implementation                     | 10       |

|          | 2.4   | Switched-Current Hilbert Transformer Design Example       | 12       |

| 3        | Rea   | ctive Power Measurement Systems                           | <b>5</b> |

|          | 3.1   | Literature Review                                         | 15       |

|          |       | 3.1.1 Hilbert transformer based methods                   | 16       |

|          |       | 3.1.2 Fast Fourier Transform based methods                | 16       |

|          |       | 3.1.3 Alternative Methods                                 | 17       |

|          |       | 3.1.4 Summary                                             | 18       |

|          | 3.2   | Reactive Power Measurement                                | 18       |

|          |       | 3.2.1 Using an ideal Hilbert transformer                  | 19       |

|          |       | -                                                         | 21       |

|          |       | 3.2.3 Measurement Method Using Two Hilbert Transformers 2 | 24       |

|          | 3.3   | Proposed Method                                           | 26       |

|          | 3.4   | Simulation Results                                        | 27       |

| 4        | Syst  | tem Level Design                                          | 82       |

|          | 4.1   | Utility Meter                                             | 32       |

|          | 4.2   | Technical Standards and Design Specifications             | 33       |

|          | 4.3  | Syster  | n Design                                                                                                                           |

|----------|------|---------|------------------------------------------------------------------------------------------------------------------------------------|

|          |      | 4.3.1   | Hilbert Transformer Design                                                                                                         |

|          |      | 4.3.2   | Coefficient Rounding                                                                                                               |

|          |      | 4.3.3   | Building Blocks Constraints                                                                                                        |

|          | 4.4  | Hardw   | vare Saving                                                                                                                        |

| <b>5</b> | Cur  | rent N  | Iemory Cell Design41                                                                                                               |

|          | 5.1  | Princi  | ple of Operation $\ldots \ldots 41$                          |

|          |      | 5.1.1   | Second-Generation current memory cell analysis 41                                                                                  |

|          |      | 5.1.2   | Loop Gain Enhancement                                                                                                              |

|          |      | 5.1.3   | Zero-Voltage Switching                                                                                                             |

|          |      | 5.1.4   | Nairn's Current Memory Cell                                                                                                        |

|          | 5.2  | Design  | $n Improvements \dots \dots$ |

|          |      | 5.2.1   | Dealing with Output Voltage                                                                                                        |

|          |      | 5.2.2   | Output Switch Voltage Drop Compensation 47                                                                                         |

|          |      | 5.2.3   | Non-linearity Errors                                                                                                               |

|          |      | 5.2.4   | Stability $\ldots \ldots 51$            |

|          |      | 5.2.5   | Amplifier and Speed                                                                                                                |

|          |      | 5.2.6   | Proposed Memory Cell                                                                                                               |

|          | 5.3  | Circui  | t Design $\ldots \ldots 54$             |

|          |      | 5.3.1   | Selecting Virtual Ground Voltage                                                                                                   |

|          |      | 5.3.2   | Choice of Input Current                                                                                                            |

|          |      | 5.3.3   | High-Linearity Differential Pair Design                                                                                            |

|          |      | 5.3.4   | Amplifier Design                                                                                                                   |

|          |      | 5.3.5   | Choice of Hold Capacitor                                                                                                           |

|          |      | 5.3.6   | Switches                                                                                                                           |

|          | 5.4  | Circui  | t Simulation Results                                                                                                               |

|          |      | 5.4.1   | Recycling Folded Cascode                                                                                                           |

|          |      | 5.4.2   | High-Linearity Differential Pair                                                                                                   |

|          |      | 5.4.3   | Proposed Memory Cell                                                                                                               |

| 6        | Cire | cuit Le | evel Design 75                                                                                                                     |

|          | 6.1  | Biasin  | g Current                                                                                                                          |

|          |      | 6.1.1   | Circuit Design                                                                                                                     |

|          |      | 6.1.2   | Circuit Simulation                                                                                                                 |

|          | 6.2  | Coeffi  | cient Gain Block                                                                                                                   |

|          |      | 6.2.1   | Circuit Design                                                                                                                     |

|          |      | 6.2.2   | Simulation Results                                                                                                                 |

|          | 6.3  | Differe | ential and Output Copy Current Mirror                                                                                              |

|          |      | 6.3.1   | Circuit Design                                                                                                                     |

|        |                                        | 6.3.2                                                                                                                   | Simulation Results                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 92                                                                                                                                                                                                       |

|--------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | 6.4                                    | Curre                                                                                                                   | nt Multiplier                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 94                                                                                                                                                                                                       |

|        |                                        | 6.4.1                                                                                                                   | Transistor Level Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                           | 96                                                                                                                                                                                                       |

|        |                                        | 6.4.2                                                                                                                   | Systematic Error Cancellation                                                                                                                                                                                                                                                                                                                                                                                                                                             | 97                                                                                                                                                                                                       |

|        |                                        | 6.4.3                                                                                                                   | Circuit Design                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 99                                                                                                                                                                                                       |

|        |                                        | 6.4.4                                                                                                                   | Circuit Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 101                                                                                                                                                                                                      |

| 7      | $\mathbf{Sys}$                         | tem Si                                                                                                                  | mulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 107                                                                                                                                                                                                      |

|        | 7.1                                    | Final                                                                                                                   | System                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 107                                                                                                                                                                                                      |

|        | 7.2                                    | Freque                                                                                                                  | ency Response                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 110                                                                                                                                                                                                      |

|        | 7.3                                    | Transi                                                                                                                  | ent Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 111                                                                                                                                                                                                      |

|        |                                        | 7.3.1                                                                                                                   | Constant Phase Difference, Variable RMS Current                                                                                                                                                                                                                                                                                                                                                                                                                           | 113                                                                                                                                                                                                      |

|        |                                        | 7.3.2                                                                                                                   | Variable Phase Difference, Constant Signal Level                                                                                                                                                                                                                                                                                                                                                                                                                          | 119                                                                                                                                                                                                      |

|        | 7.4                                    | Non-s                                                                                                                   | inusoidal Input (Wideband Signal)                                                                                                                                                                                                                                                                                                                                                                                                                                         | 120                                                                                                                                                                                                      |

|        | 7.5                                    | Monte                                                                                                                   | Carlo simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 122                                                                                                                                                                                                      |

| 8      | Cor                                    | nclusio                                                                                                                 | n and Future Work                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 126                                                                                                                                                                                                      |

|        | 8.1                                    |                                                                                                                         | e Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                          |

|        |                                        |                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                          |

| Bi     | hling                                  | graphy                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 128                                                                                                                                                                                                      |

| DI     | 51108                                  | Stapity                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                          |

|        |                                        |                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 136                                                                                                                                                                                                      |

|        | Tra                                    |                                                                                                                         | Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                          |

| A      | Tra<br>Der                             | nsistor<br>•ivatior                                                                                                     | Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $136\\139$                                                                                                                                                                                               |

| A      | Tra<br>Der                             | nsistor<br>rivation<br>Wide                                                                                             | · Parameters<br>ns                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>136</b><br><b>139</b><br>139                                                                                                                                                                          |

| A      | Tra<br>Der                             | nsistor<br>ivation<br>Wide<br>B.1.1                                                                                     | • <b>Parameters</b><br>ns<br>Swing Cascode Current Mirror                                                                                                                                                                                                                                                                                                                                                                                                                 | <ul> <li><b>136</b></li> <li><b>139</b></li> <li>141</li> </ul>                                                                                                                                          |

| A      | Tra<br>Der                             | nsistor<br>ivation<br>Wide<br>B.1.1<br>B.1.2                                                                            | • Parameters<br>ns<br>Swing Cascode Current Mirror                                                                                                                                                                                                                                                                                                                                                                                                                        | <ul> <li><b>136</b></li> <li><b>139</b></li> <li>141</li> <li>142</li> </ul>                                                                                                                             |

| A      | Tra<br>Der<br>B.1                      | nsistor<br>ivation<br>Wide<br>B.1.1<br>B.1.2<br>Differe                                                                 | • Parameters ns Swing Cascode Current Mirror                                                                                                                                                                                                                                                                                                                                                                                                                              | <ul> <li><b>136</b></li> <li><b>139</b></li> <li>141</li> <li>142</li> <li>143</li> </ul>                                                                                                                |

| A      | Tra<br>Der<br>B.1<br>B.2               | nsistor<br>ivation<br>Wide<br>B.1.1<br>B.1.2<br>Differe                                                                 | • Parameters         ns         Swing Cascode Current Mirror         Case 1: (B.16) is stronger than (B.15)         Case 2: (B.14) is stronger than (B.13)         ential Pair Transconductance                                                                                                                                                                                                                                                                           | <ul> <li><b>136</b></li> <li><b>139</b></li> <li>141</li> <li>142</li> <li>143</li> <li>144</li> </ul>                                                                                                   |

| A      | Tra<br>Der<br>B.1<br>B.2<br>B.3        | nsistor<br>ivation<br>Wide<br>B.1.1<br>B.1.2<br>Differe<br>Curre                                                        | • Parameters ns Swing Cascode Current Mirror                                                                                                                                                                                                                                                                                                                                                                                                                              | <ul> <li><b>136</b></li> <li><b>139</b></li> <li>141</li> <li>142</li> <li>143</li> <li>144</li> </ul>                                                                                                   |

| A<br>B | Tra<br>Der<br>B.1<br>B.2<br>B.3        | nsistor<br>Vide<br>B.1.1<br>B.1.2<br>Differe<br>Curre<br>B.3.1<br>or Ana                                                | • Parameters ns Swing Cascode Current Mirror                                                                                                                                                                                                                                                                                                                                                                                                                              | <ul> <li><b>136</b></li> <li><b>139</b></li> <li>141</li> <li>142</li> <li>143</li> <li>144</li> <li>146</li> <li><b>149</b></li> </ul>                                                                  |

| A<br>B | Tra<br>Der<br>B.1<br>B.2<br>B.3<br>Err | nsistor<br>Vide<br>B.1.1<br>B.1.2<br>Differe<br>Curre<br>B.3.1<br>or Ana                                                | • Parameters ns Swing Cascode Current Mirror                                                                                                                                                                                                                                                                                                                                                                                                                              | <ul> <li><b>136</b></li> <li><b>139</b></li> <li>141</li> <li>142</li> <li>143</li> <li>144</li> <li>146</li> <li><b>149</b></li> <li>150</li> </ul>                                                     |

| A<br>B | Tra<br>Der<br>B.1<br>B.2<br>B.3<br>Err | nsistor<br>Vide<br>B.1.1<br>B.1.2<br>Differe<br>Curre<br>B.3.1<br>or Ana<br>Non-Ie                                      | • Parameters  IS Swing Cascode Current Mirror                                                                                                                                                                                                                                                                                                                                                                                                                             | <ol> <li>136</li> <li>139</li> <li>141</li> <li>142</li> <li>143</li> <li>144</li> <li>146</li> <li>149</li> <li>150</li> <li>150</li> </ol>                                                             |

| A<br>B | Tra<br>Der<br>B.1<br>B.2<br>B.3<br>Err | nsistor<br>Vide<br>B.1.1<br>B.1.2<br>Differe<br>Curre:<br>B.3.1<br>or Ana<br>Non-Ie<br>C.1.1                            | Parameters      S      Swing Cascode Current Mirror                                                                                                                                                                                                                                                                                                                                                                                                                       | <ul> <li><b>136</b></li> <li><b>139</b></li> <li>141</li> <li>142</li> <li>143</li> <li>144</li> <li>146</li> <li><b>149</b></li> <li>150</li> <li>150</li> <li>150</li> <li>152</li> </ul>              |

| A<br>B | Tra<br>Der<br>B.1<br>B.2<br>B.3<br>Err | nsistor<br>Vide<br>B.1.1<br>B.1.2<br>Differe<br>Curre:<br>B.3.1<br>or Ana<br>Non-Ie<br>C.1.1<br>C.1.2                   | Parameters      S      Swing Cascode Current Mirror                                                                                                                                                                                                                                                                                                                                                                                                                       | <ul> <li><b>136</b></li> <li><b>139</b></li> <li>141</li> <li>142</li> <li>143</li> <li>144</li> <li>146</li> <li><b>149</b></li> <li>150</li> <li>150</li> <li>152</li> <li>153</li> </ul>              |

| A<br>B | Tra<br>Der<br>B.1<br>B.2<br>B.3<br>Err | nsistor<br>Vide<br>B.1.1<br>B.1.2<br>Differe<br>Curre<br>B.3.1<br>or Ana<br>Non-Ie<br>C.1.1<br>C.1.2<br>C.1.3           | <b>Parameters ns</b> Swing Cascode Current Mirror         Case 1: (B.16) is stronger than (B.15)         Case 2: (B.14) is stronger than (B.13)         Case 2: (B.14) is stronger than (B.13)         ential Pair Transconductance         Int Squarer         Biasing Current Limits <b>Uysis</b> deal Effects on Building Blocks         Current Memory Cell         Differential Current Mirror         Output Copy Current Mirror                                    | <ul> <li><b>136</b></li> <li><b>139</b></li> <li>141</li> <li>142</li> <li>143</li> <li>144</li> <li>146</li> <li><b>149</b></li> <li>150</li> <li>150</li> <li>152</li> <li>153</li> <li>154</li> </ul> |

| A<br>B | Tra<br>Der<br>B.1<br>B.2<br>B.3<br>Err | nsistor<br>Vide<br>B.1.1<br>B.1.2<br>Differe<br>Curres<br>B.3.1<br>or Ana<br>Non-Ie<br>C.1.1<br>C.1.2<br>C.1.3<br>C.1.4 | <b>Parameters hs</b> Swing Cascode Current Mirror         Case 1: (B.16) is stronger than (B.15)         Case 2: (B.14) is stronger than (B.13)         Case 2: (B.14) is stronger than (B.13)         ential Pair Transconductance         Int Squarer         Biasing Current Limits         Biasing Current Limits         Current Memory Cell         Differential Current Mirror         Output Copy Current Mirror         From Building Blocks to All-Pass Section | <ul> <li><b>136</b></li> <li><b>139</b></li> <li>141</li> <li>142</li> <li>143</li> <li>144</li> <li>146</li> <li><b>149</b></li> <li>150</li> <li>150</li> <li>152</li> <li>153</li> <li>154</li> </ul> |

| D | $\operatorname{Mis}$ | match on Transistors                         | 162   |   |

|---|----------------------|----------------------------------------------|-------|---|

|   | D.1                  | Propagation of Uncertainty                   | 162   | ) |

|   | D.2                  | Pelgrom Models for Mismatch                  | 163   |   |

|   | D.3                  | Mismatch on a Current Mirror                 | . 164 | : |

|   | D.4                  | Differential Pair Transconductance Variation | 166   | i |

|   | D.5                  | Differential Pair Input Offset Voltage       | 169   | I |

|   | D.6                  | Differential Current Mirror Gain Error       | . 170 | I |

|   | D.7                  | Differential Current Mirror Offset Current   | . 172 | ; |

# List of Figures

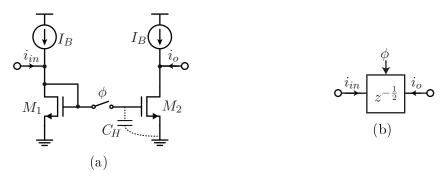

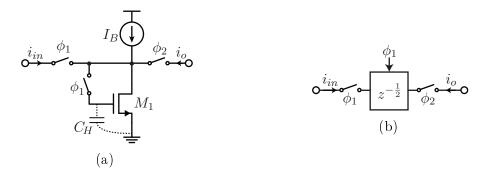

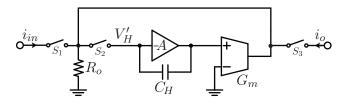

| 1.1 | Second generation current memory cell. (a) Circuit and (b) Block representation. | 3  |

|-----|----------------------------------------------------------------------------------|----|

| 1.2 | Second generation current memory cell. (a) Circuit and (b) Block                 |    |

|     | representation.                                                                  | 3  |

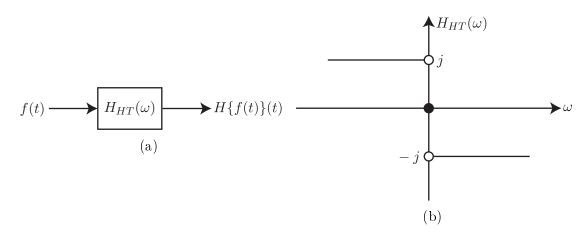

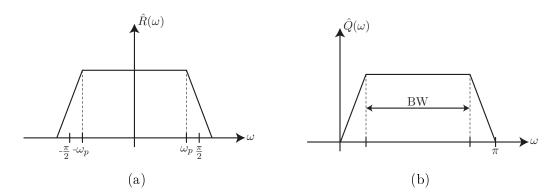

| 2.1 | (a) Hilbert transformer filter. (b) Frequency response of the Hilbert            |    |

|     | transformer                                                                      | 6  |

| 2.2 | Hilbert transformer implementation using all-pass transfer functions.            | 9  |

| 2.3 | Relationship between (a) half-band filter cutoff frequency $\omega_p$ and (b)    |    |

|     | Hilbert transformer bandwidth BW                                                 | 9  |

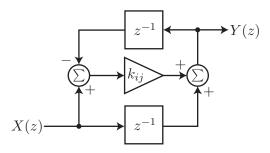

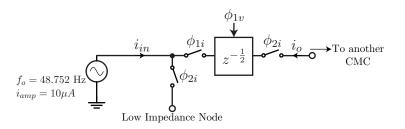

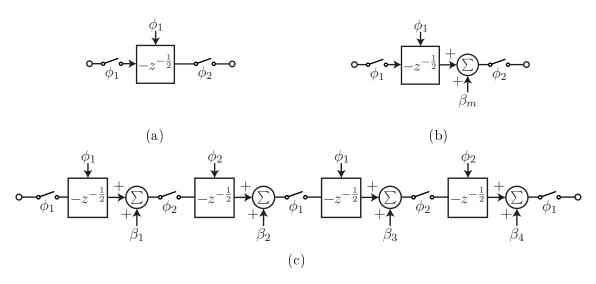

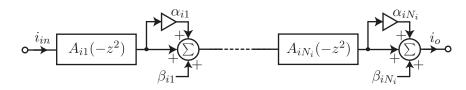

| 2.4 | Block diagram of a first-order structurally all-pass section                     | 10 |

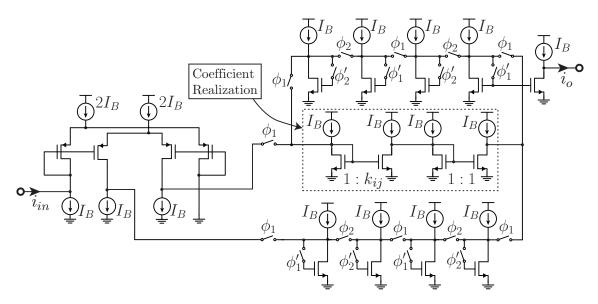

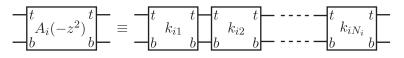

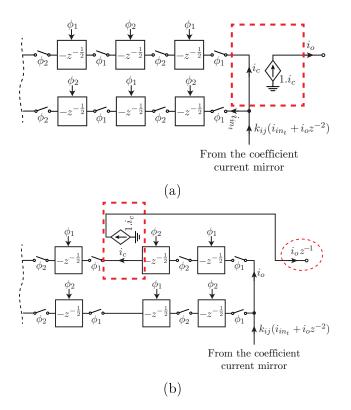

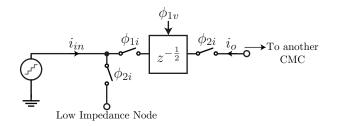

| 2.5 | Block diagram of an one-coefficient switched-current structurally all-           |    |

|     | pass section                                                                     | 11 |

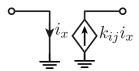

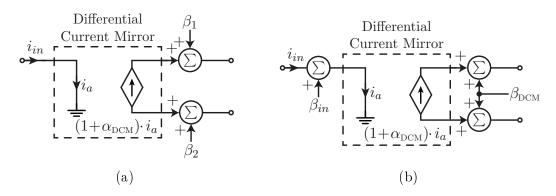

| 2.6 | Differential Current Mirror implementation.                                      | 11 |

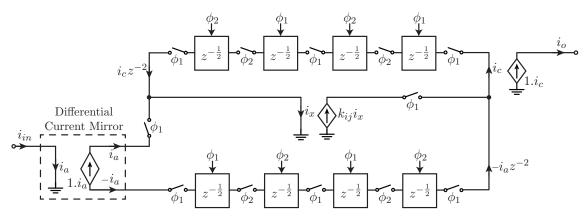

| 2.7 | Switched-current circuit implementation of a Structurally All-Pass               |    |

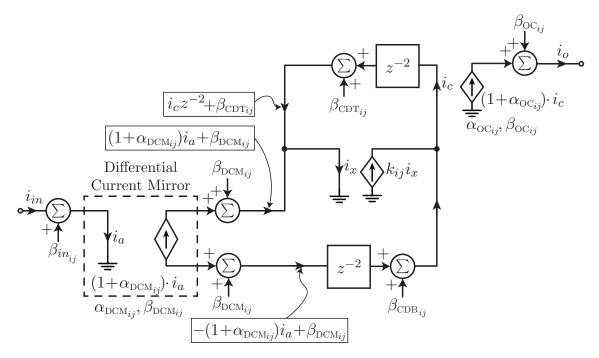

|     | Section.                                                                         | 12 |

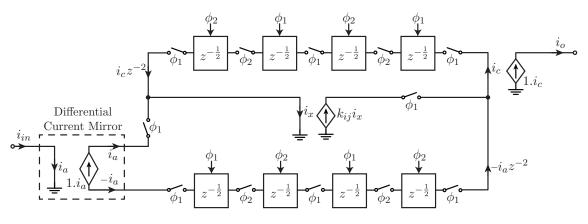

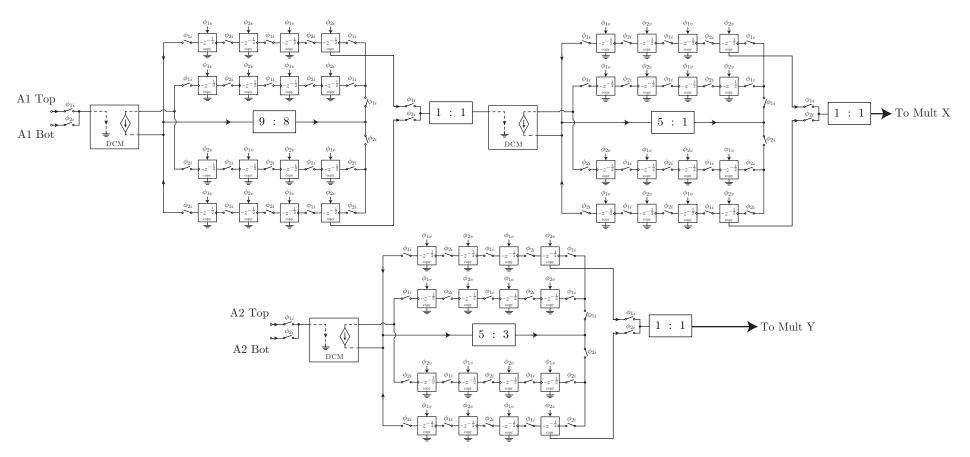

| 2.8 | Switched-current implementation of the Hilbert transformer                       | 13 |

| 2.9 | Phase response of the Hilbert transformer                                        | 14 |

| 3.1 | Reactive power measurement system using one Hilbert transformer                  | 19 |

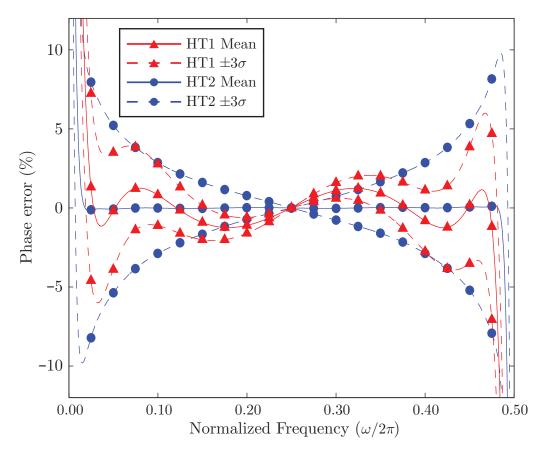

| 3.2 | Phase error around the $90^{\circ}$ phase shift for different Hilbert trans-     |    |

|     | formers. Monte Carlo analysis adopting a $1\%$ variation on each struc-          |    |

|     | turally all-pass section coefficient.                                            | 23 |

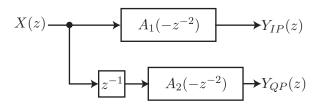

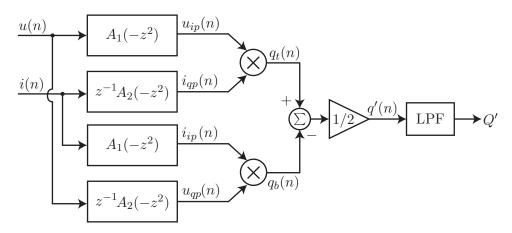

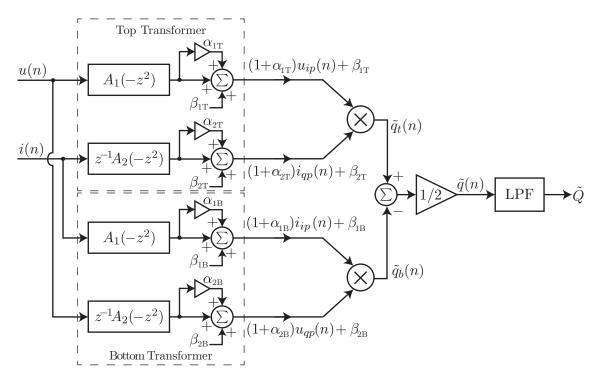

| 3.3 | Reactive Power measurement using two Hilbert transformers                        | 24 |

| 3.4 | Block diagram of a one-coefficient switched-current structurally all-            |    |

|     | pass section                                                                     | 26 |

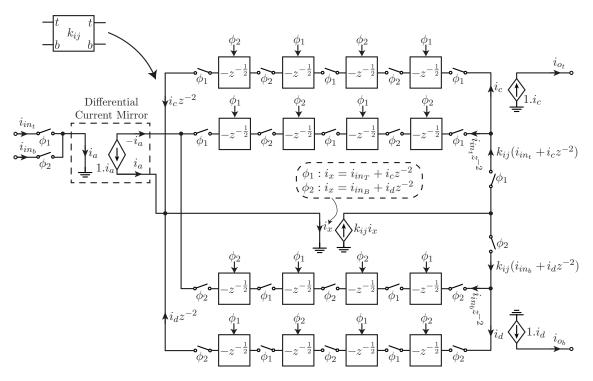

| 3.5 | Block diagram of two switched-current structurally all-pass sections             |    |

|     | with shared coefficients.                                                        | 27 |

| 3.6 | Representation of the all-pass transfer function with a cascade of               |    |

|     | shared coefficient SAPS.                                                         | 27 |

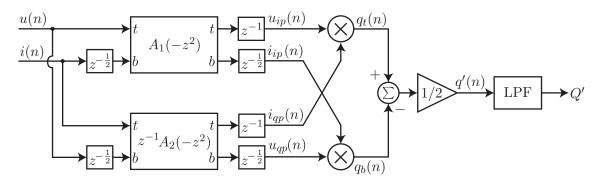

| 3.7 | Final measurement system proposed in this work                                   | 28 |

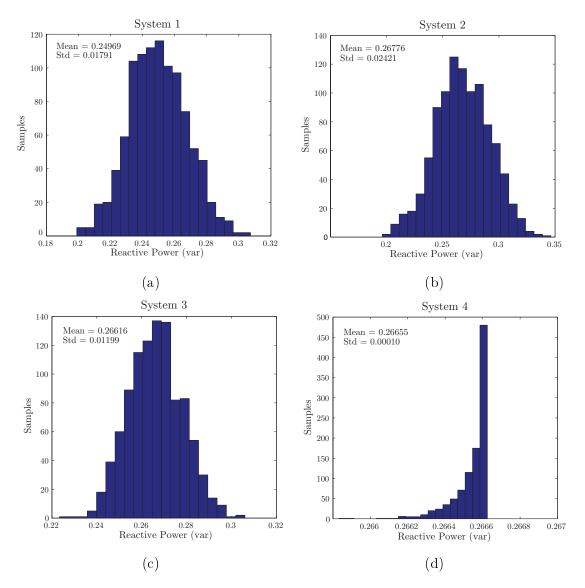

| 3.8        | Histogram of reactive power measurement for each system                             | 30  |

|------------|-------------------------------------------------------------------------------------|-----|

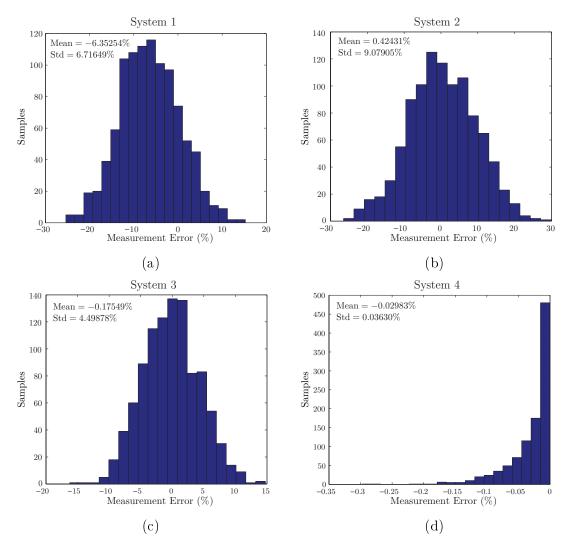

| 3.9        | Histogram of measurement relative error for each system                             | 31  |

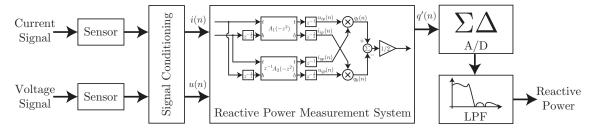

| 4.1        | Block diagram of the Utility Meter                                                  | 32  |

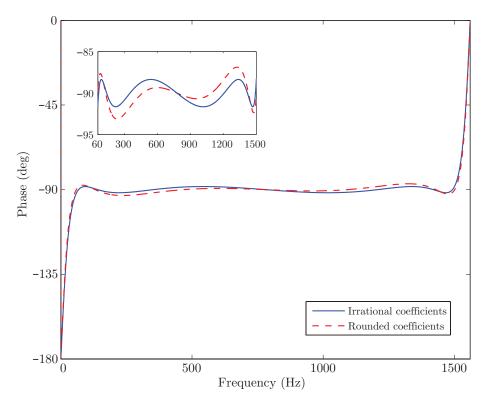

| 4.2        | Phase comparison between ideal and rounded coefficients                             | 37  |

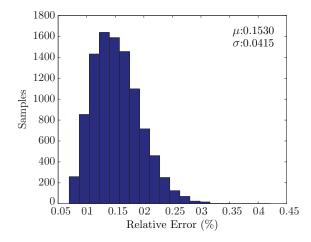

| 4.3        | Histogram with the maximum relative error of the system obtained                    |     |

|            | with 10000 Monte Carlo simulations.                                                 | 39  |

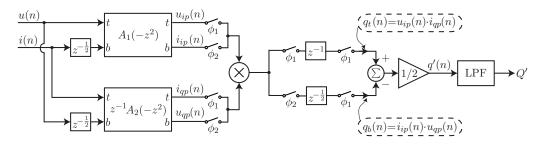

| 4.4        | Reactive power measurement system with a shared multiplier. $\ldots$ .              | 40  |

| 4.5        | A cut from the structurally all-pass filter copying the output signal               |     |

|            | (a) and copying a delayed version of the output signal (b). $\ldots$ .              | 40  |

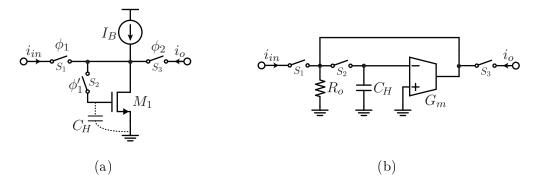

| 5.1        | Second-generation current memory cell circuit (a) and small-signal                  |     |

|            | model (b)                                                                           | 42  |

| 5.2        | Second-generation current memory cell during sampling phase $(\phi_1)$ .            |     |

|            | Small-signal model (a) and block diagram representation (b)                         | 42  |

| 5.3        | Small-signal model of a second-generation current memory cell during                |     |

|            | holding phase $(\phi_2)$                                                            | 43  |

| 5.4        | Lopp-gain enhancement by introducing a voltage amplifier                            | 44  |

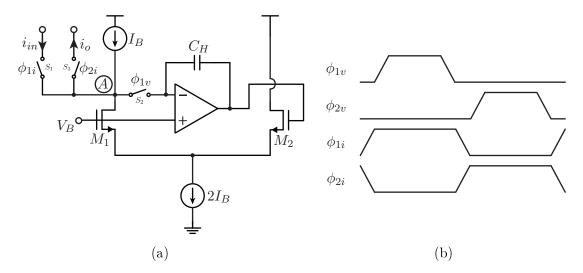

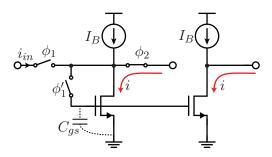

| 5.5        | Circuit representation of a Zero-Voltage switching current memory cell.             | 44  |

| 5.6        | Circuit implementation of Nairn's current memory cell (a) and its                   |     |

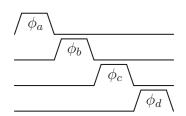

|            | switching sequence (b)                                                              | 45  |

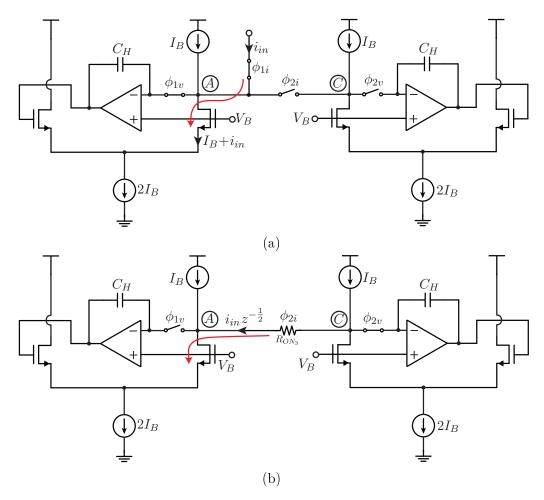

| 5.7        | Cascade of two current memory cells, with the left one operating on                 |     |

| <b>F</b> 0 | sampling phase (a) and holding phase (b)                                            | 47  |

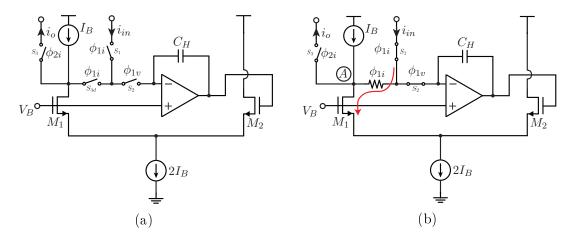

| 5.8        | Current memory cell with dummy switch $S_{3d}$ (a) and current path                 | 4.0 |

| 50         | during sampling phase (b)                                                           | 48  |

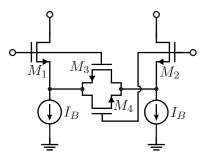

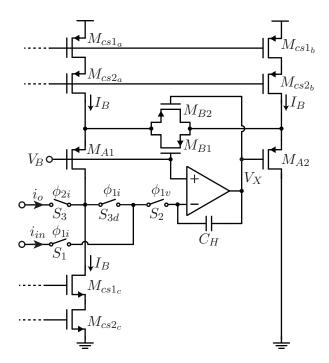

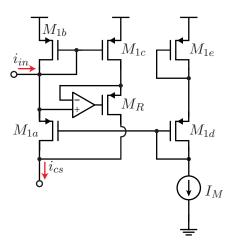

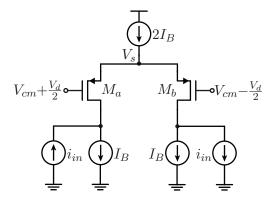

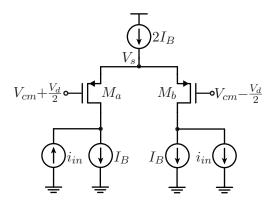

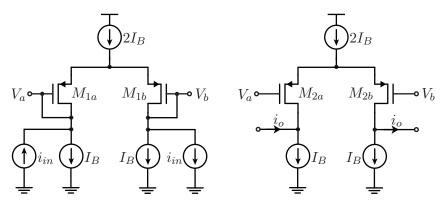

| 5.9        | High-linearity differential pair.                                                   | 51  |

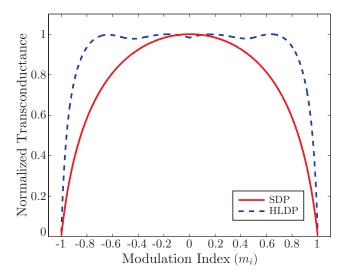

|            | Normalized transconductance vs modulation index                                     | 51  |

| 5.11       | Small-signal model of a zero-voltage switching current memory cell                  | ۲ 1 |

| F 10       | with parasitic components.                                                          | 51  |

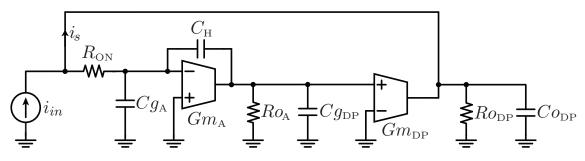

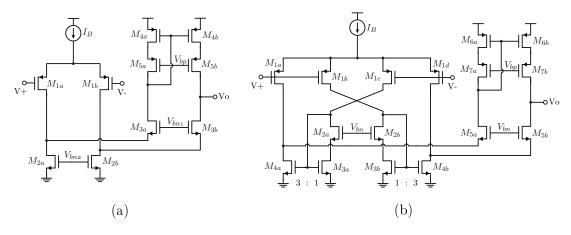

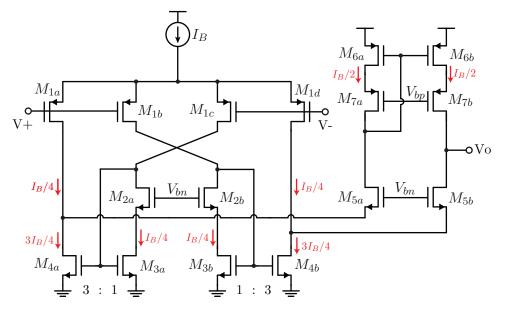

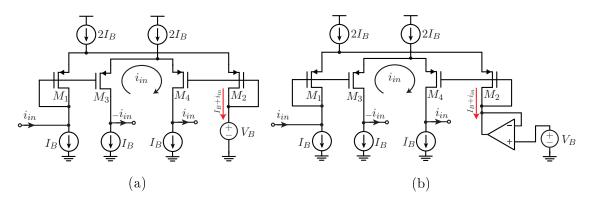

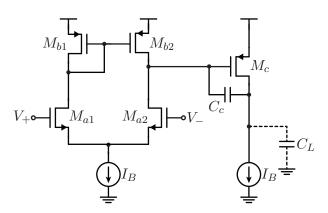

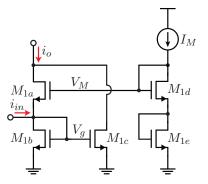

| 5.12       | Voltage amplifiers topology, Folded Cascode (a) and Recycling Folded<br>Cascode (b) | 53  |

| 5.13       | Proposed current memory cell, with a high-linearity differential pair               |     |

|            | implemented with PMOS transistors.                                                  | 54  |

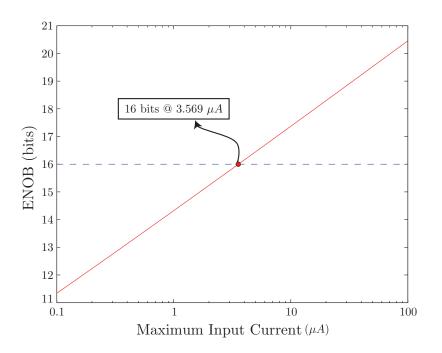

| 5.14       | Effective number of bits (ENOB) vs maximum input current                            | 57  |

|            | Recycling Folded Cascode amplifier with current paths on small-signal               |     |

|            | operation                                                                           | 59  |

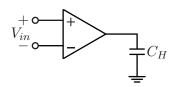

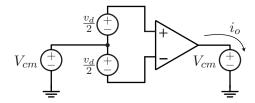

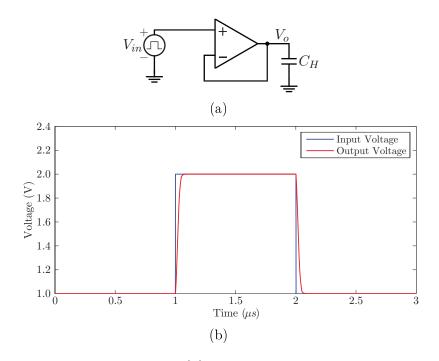

| 5.16       | AC Sweep simulation setup.                                                          | 63  |

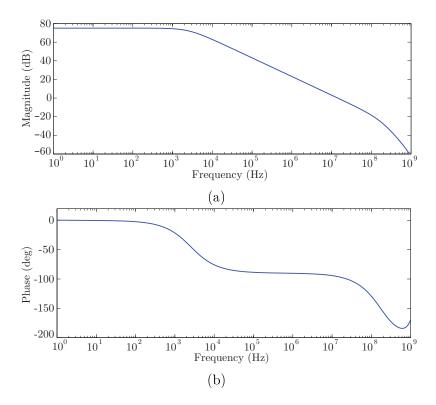

|            | Magnitude (a) and Phase (b) plots for the recycling folded cascode.                 | 63  |

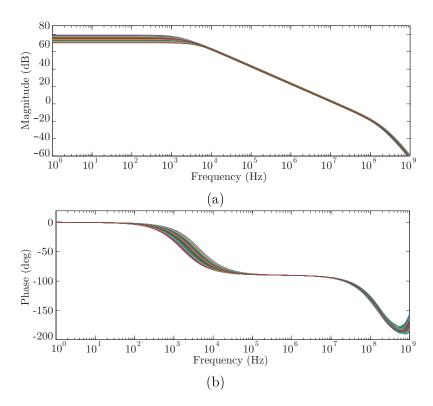

| 5.18       | Magnitude (a) and Phase (b) plots for all Monte Carlo simulations of                |     |

|            | the recycling folded cascode                                                        | 64  |

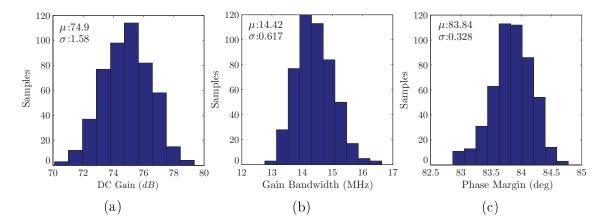

| 5.19 | Histogram of Monte Carlo simulation resultant data for DC Gain (a),       |    |

|------|---------------------------------------------------------------------------|----|

|      | Gain Bandwidth (b) and Phase Margin (c).                                  | 64 |

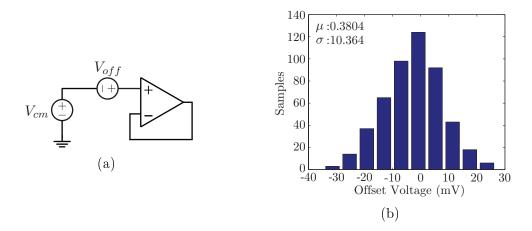

| 5.20 | DC Sweep simulation setup.                                                | 65 |

| 5.21 | Plot of amplifier's output current (a) and transconductance (b) vs        |    |

|      | input differential voltage.                                               | 65 |

| 5.22 | Slew rate test setup (a) and plot of amplifier's step response (b)        | 65 |

|      | Offset Monte Carlo simulation setup (b) and histogram of the resul-       |    |

|      | tant data (b).                                                            | 66 |

| 5.24 | Plot of high-linearity differential pair output current (a) and transcon- |    |

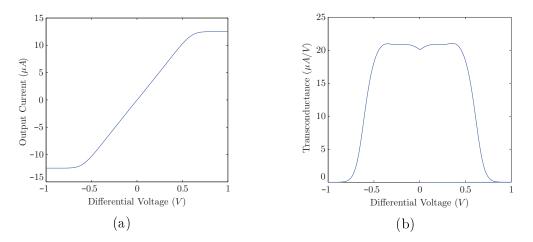

|      | ductance (b) vs input differential voltage                                | 67 |

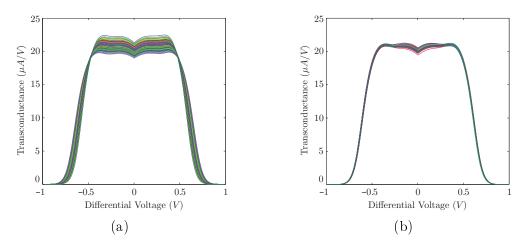

| 5.25 | Monte Carlo results of the high-linearity differential pair transcon-     |    |

|      | ductance curve under process parameters variation (a) and mismatch        |    |

|      | (b)                                                                       | 67 |

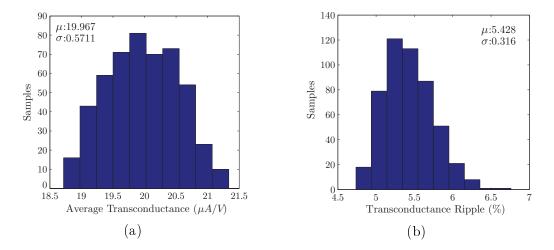

| 5.26 | Histogram of Monte Carlo simulation resultant data for average            |    |

|      | transconductance(a) and transconductance ripple (b)                       | 68 |

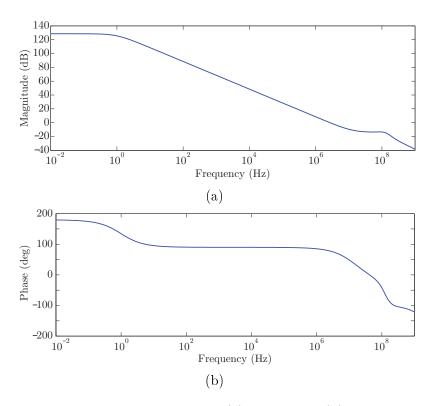

| 5.27 | Open-loop magnitude (a) and phase (b) characteristics                     | 69 |

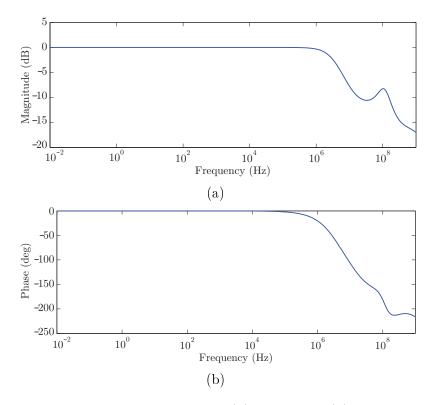

|      | Closed-loop magnitude (a) and phase (b) characteristics.                  | 69 |

|      | Current memory cell static test setup                                     | 70 |

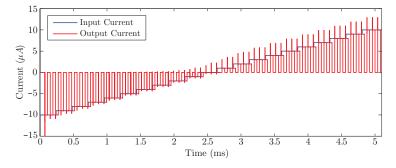

|      | Transient response of the static test.                                    | 70 |

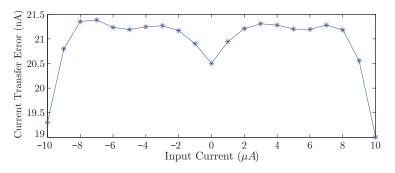

|      | Current transfer error $(i_o - i_{in})$ vs input current $(i_{in})$ .     | 70 |

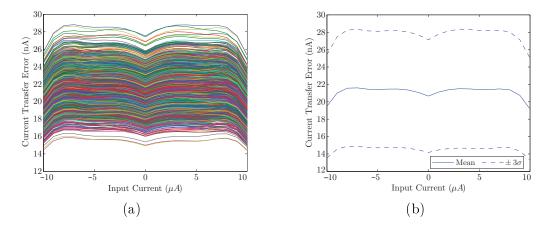

|      | Monte Carlo results of the current transfer error curve (a) and its       |    |

|      | statistical variations (b).                                               | 71 |

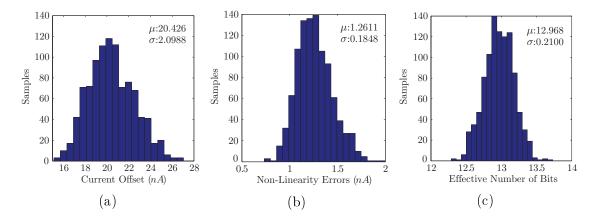

| 5.33 | Histogram of Monte Carlo simulation resultant data for current offset     |    |

|      | (a), non-linearity errors (b) and effective number of bits (c)            | 71 |

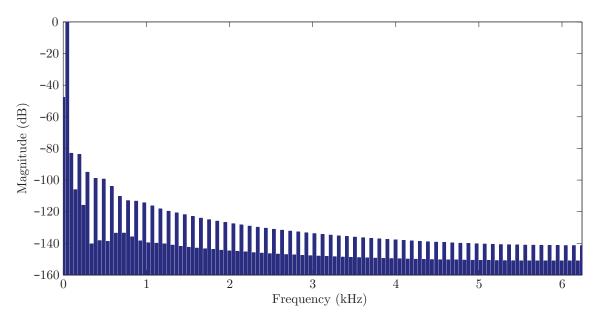

| 5.34 | Current memory cell dynamic test setup                                    | 72 |

|      | Transient response of the dynamic test.                                   | 72 |

| 5.36 | Sampled output of the dynamic test.                                       | 73 |

| 5.37 | Magnitude response of the sampled output fast Fourier transform           | 73 |

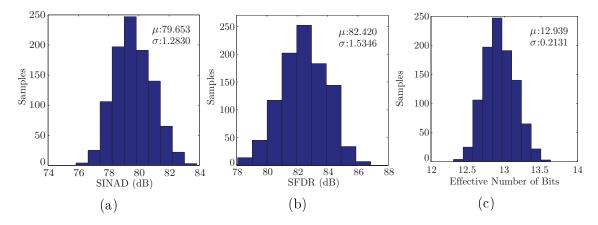

|      | Histograms of Monte Carlo simulation resultant data for signal-to-        |    |

|      | noise-and-distortion ratio (a), spurious-free dynamic range (b) and       |    |

|      | effective number of bits (c).                                             | 74 |

|      |                                                                           |    |

| 6.1  | Circuit implementation of the biasing currents                            | 76 |

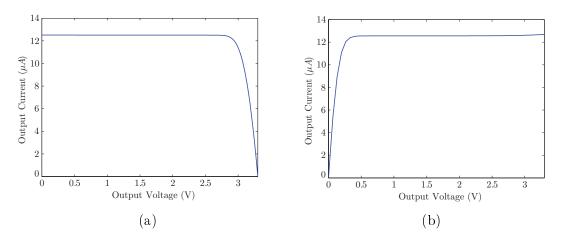

| 6.2  | DC Sweep of the output voltage for (a) PMOS biasing current and           |    |

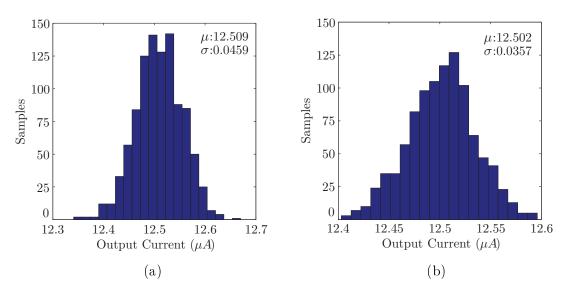

|      | (b) NMOS biasing current                                                  | 78 |

| 6.3  | Histogram of the Monte Carlo simulation resultant data for the out-       |    |

|      | put current of (a) PMOS biasing current with $Vop = 2.1$ and (b)          |    |

|      | NMOS biasing current with $Von = 1.1. \dots \dots \dots \dots \dots$      | 78 |

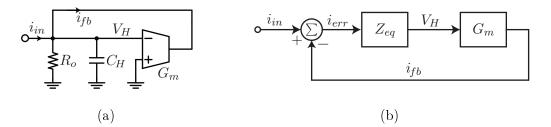

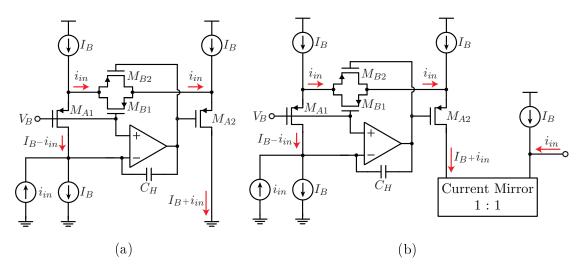

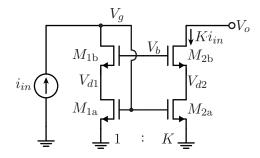

| 6.4  | Coefficient gain block ideal implementation.                              | 79 |

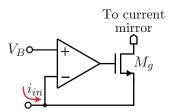

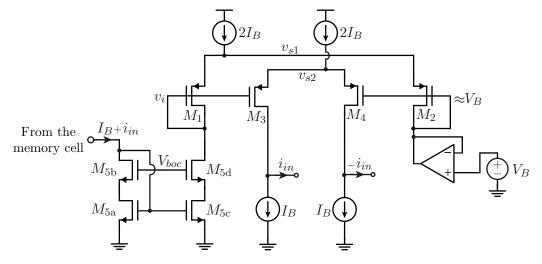

| 6.5 Current conveyor to implement input virtual ground                                                                                 | 79         |

|----------------------------------------------------------------------------------------------------------------------------------------|------------|

| 6.6 Coefficient gain block complete circuit with (a) $2k_{ij}I_B$ biasing current                                                      |            |

| at the output and (b) with current mirror to implement the current                                                                     | 80         |

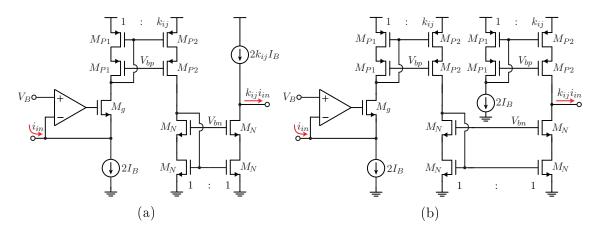

| 6.7 Simulation results for the output current with a DC sweep of input                                                                 |            |

| current for coefficient (a) $k_{11} = 8/9$ , (b) $k_{12} = 1/5$ and (c) $k_{21} = 3/5$ .                                               | 83         |

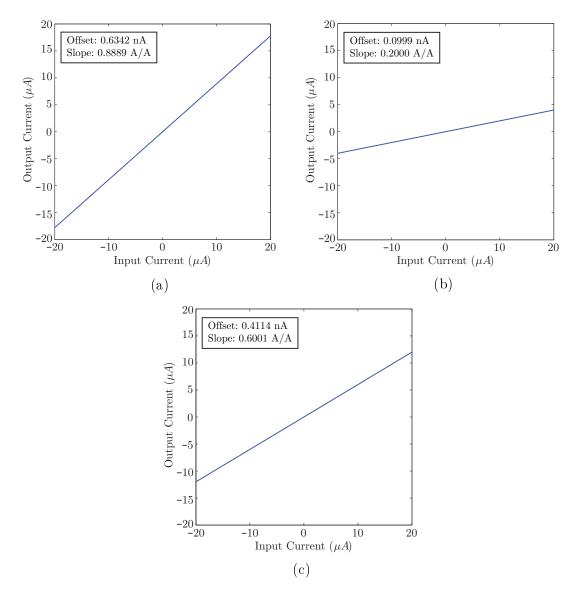

| 6.8 Frequency response for coefficient (a) $k_{11} = 8/9$ , (b) $k_{12} = 1/5$ and                                                     |            |

| (c) $k_{21} = 3/5$                                                                                                                     | 84         |

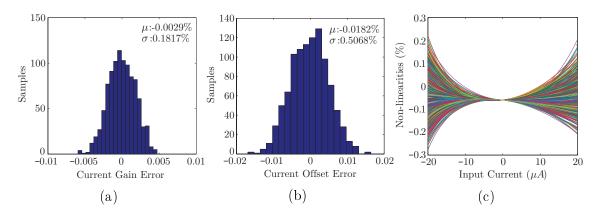

| 6.9 Results for Monte Carlo simulation for coefficient $k_{11} = 8/9$ . (a) Gain                                                       | ~ ~        |

| error, (b) Offset error and (c) Non-linearity errors. $\dots \dots \dots$                                                              | 85         |

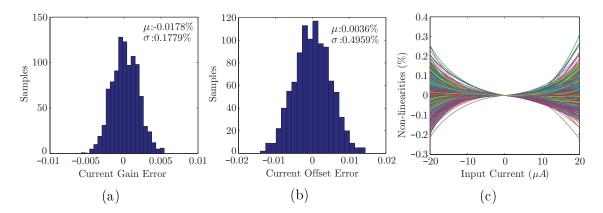

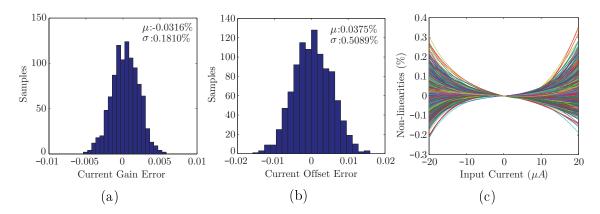

| 6.10 Results for Monte Carlo simulation for coefficient $k_{12} = 1/5$ . (a) Gain arrow (b) Offset arrow and (c) Non linearity arrows  | <u>و ج</u> |

| error, (b) Offset error and (c) Non-linearity errors                                                                                   | 85         |

| 6.11 Results for Monte Carlo simulation for coefficient $k_{21} = 3/5$ . (a) Gain error, (b) Offset error and (c) Non-linearity errors | 85         |

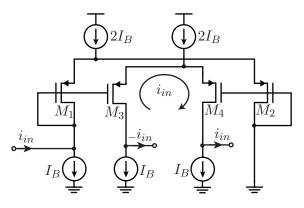

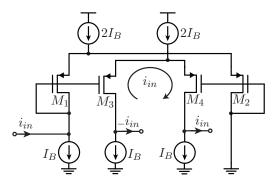

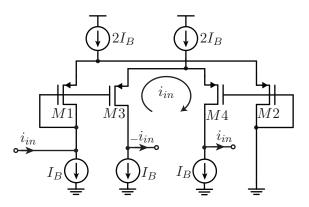

| 6.12 Differential current mirror ideal implementation.                                                                                 | 86         |

| 6.13 Differential current mirror implementation with (a) low-impedance                                                                 | 00         |

| biasing voltage and (b) voltage buffer                                                                                                 | 87         |

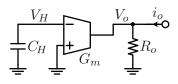

| 6.14 Output copy of an ideal current memory cell.                                                                                      | 87         |

| 6.15 (a) Current flow of the zero-voltage switching current memory cell                                                                |            |

| and (b) stored current copy                                                                                                            | 87         |

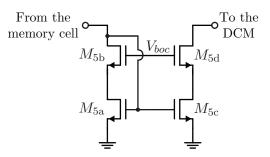

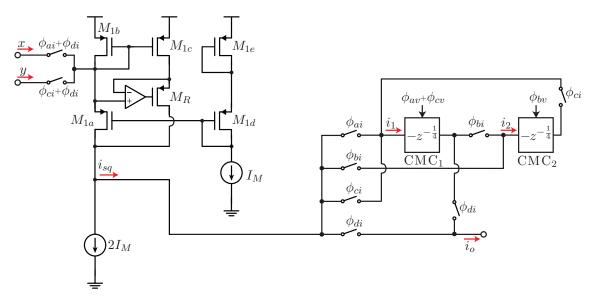

| 6.16 Output copy current mirror circuit implementation                                                                                 | 88         |

| 6.17 Single-block implementation of both differential current mirror and                                                               |            |

| output copy current mirror.                                                                                                            | 88         |

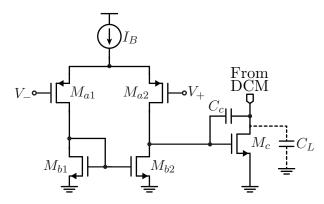

| 6.18 Circuit implementation of the differential current mirror amplifier                                                               | 91         |

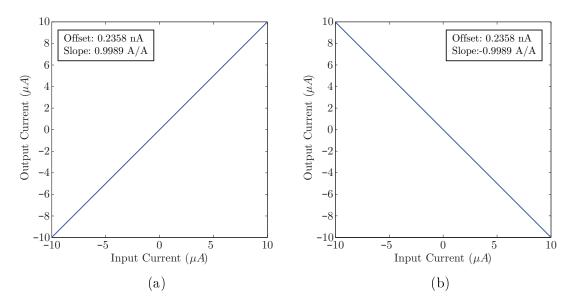

| 6.19 Results for a DC sweep of the input current for (a) positive output                                                               |            |

| current and (b) negative output current.                                                                                               | 92         |

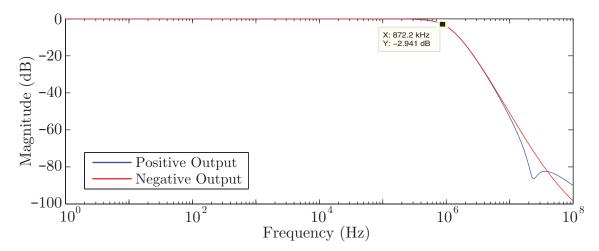

| 6.20 Frequency response for positive output (blue trace) and negative out-                                                             |            |

| put (red trace). $\dots$                                       |            |

| 6.21 Monte Carlo simulation results for both outputs                                                                                   | 93         |

| 6.22 Results for Monte Carlo simulation for the positive output. (a) Gain                                                              | 0.4        |

| error, (b) Offset error and (c) Non-linearity errors                                                                                   | 94         |

| error, (b) Offset error and (c) Non-linearity errors.                                                                                  | 94         |

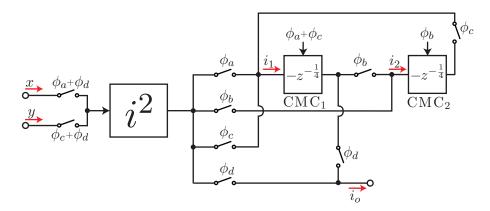

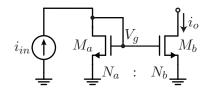

| 6.24 Current multiplier basic behavior.                                                                                                |            |

| 6.25 Current multiplier switching sequence.                                                                                            |            |

| 6.26 Current squarer circuit implementation                                                                                            |            |

| 6.27 Complete circuit implementation of the current multiplier                                                                         |            |

| 6.28 Circuit implementation of the regulated cascode amplifier                                                                         |            |

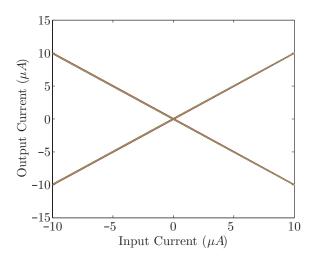

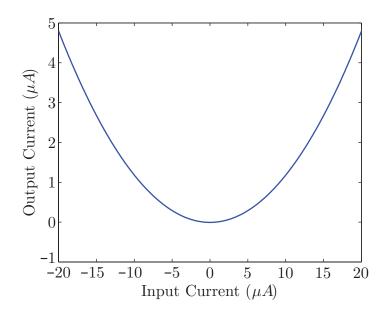

| 6.29 Output current result for a DC sweep of the input current                                                                         | 102        |

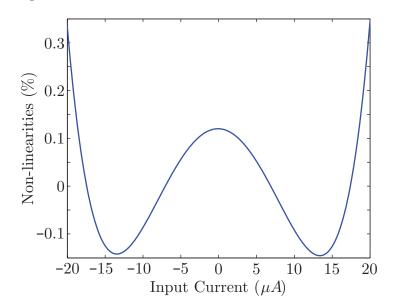

| 6.30 Non-linearity errors for the current squarer. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                        | 102        |

|                                                                                                                                        |            |

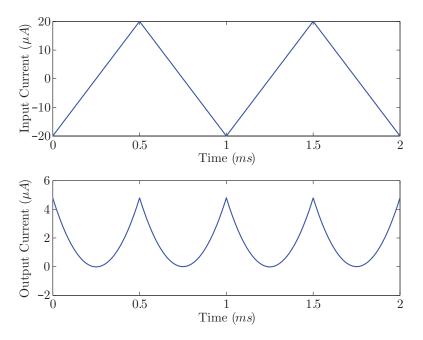

| 6.31 | Transient results for an $1kHz$ saw-tooth input                                                                                                                | 3 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

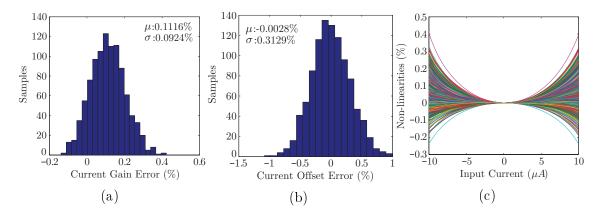

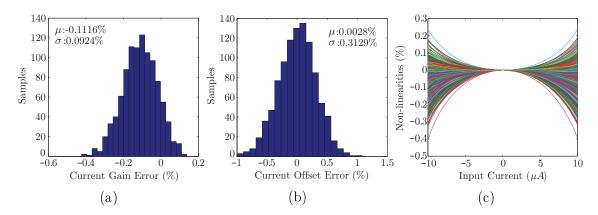

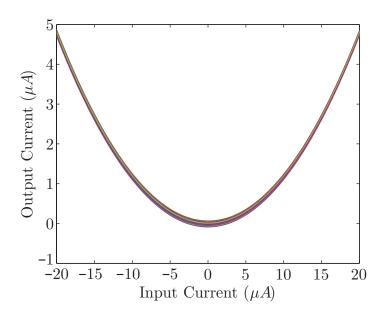

| 6.32 | Monte Carlo result for the current transfer curve of the current squarer.103                                                                                   | 3 |

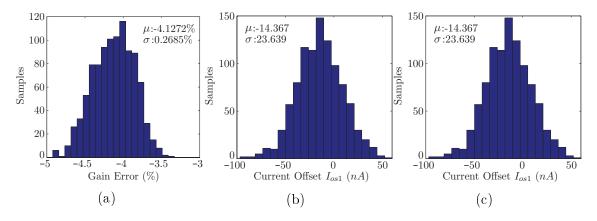

| 6.33 | Histograms for the curve fit of the Monte Carlo simulation resultant                                                                                           |   |

|      | data. (a) Gain error $\alpha_M$ , (b) Current offset $I_{os1}$ and (c) Current offset                                                                          |   |

|      | $I_{os2}$                                                                                                                                                      | 1 |

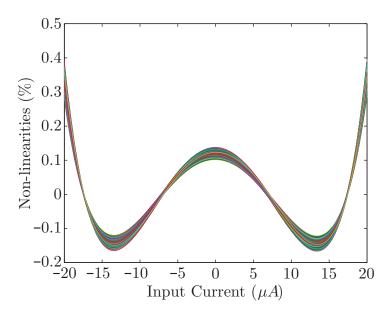

| 6.34 | Monte Carlo results for the non-linearity errors                                                                                                               | 1 |

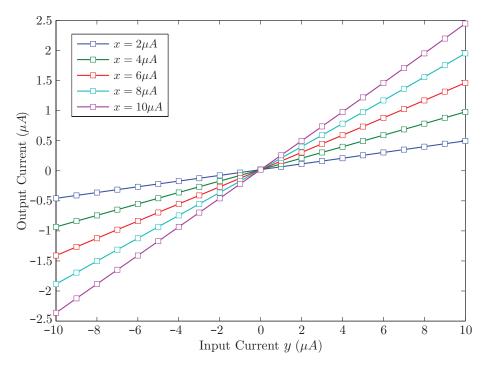

| 6.35 | Simulated transfer characteristics of the current multiplier, $i_o$ vs. $y$ .                                                                                  |   |

|      | x is kept constant at different levels detailed by plot legend 105                                                                                             | 5 |

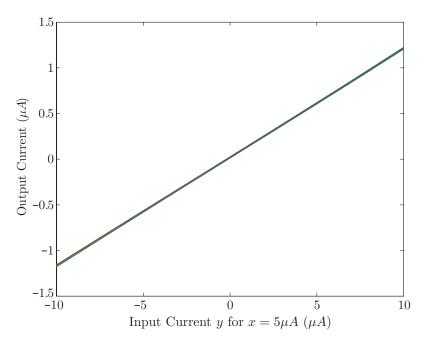

| 6.36 | Monte Carlo simulation results of the transfer characteristics of $i_o$ vs.                                                                                    |   |

|      | $y$ when $x = 5\mu A$                                                                                                                                          | 5 |

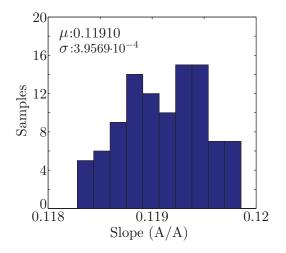

| 6.37 | Histogram of the slope obtained for each Monte Carlo output sample. 100                                                                                        |   |

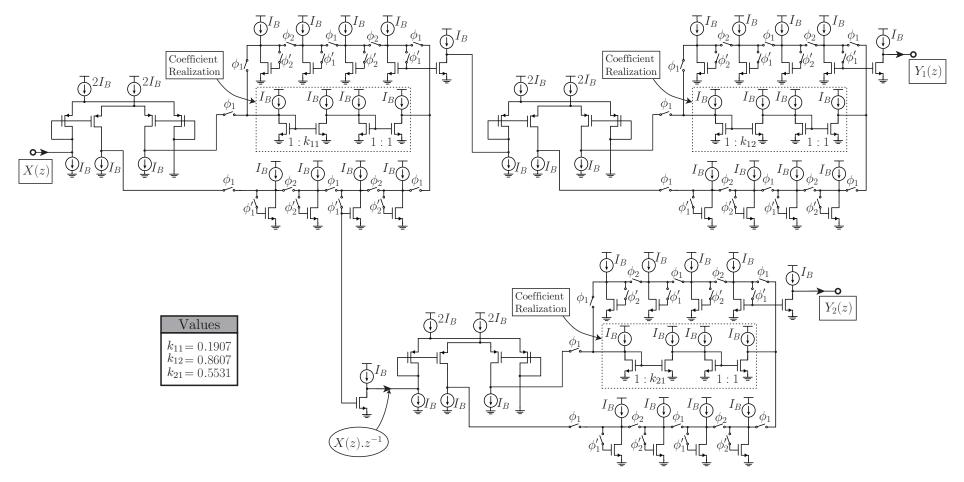

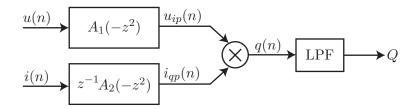

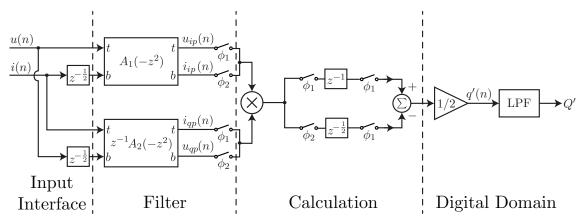

| 7.1  | Reactive power measurement system block diagram                                                                                                                | 7 |

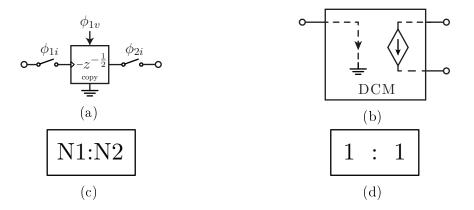

| 7.2  | Representation of each circuit block. (a) Current Memory Cell, (b)                                                                                             |   |

|      | Differential Current Mirror, (c) Coefficient Gain Block and (d) Out-                                                                                           |   |

|      | put Copy Current Mirror                                                                                                                                        | 3 |

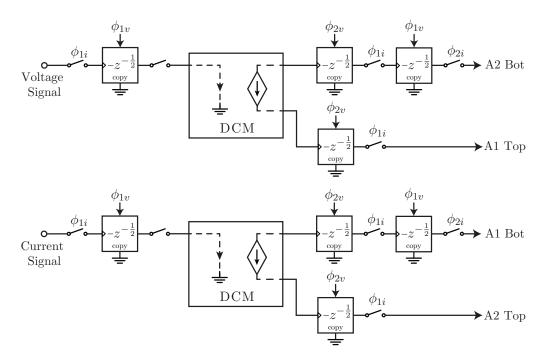

| 7.3  | Reactive power measurement system input interface diagram 108                                                                                                  | 3 |

| 7.4  | Reactive power measurement system filter diagram                                                                                                               | ) |

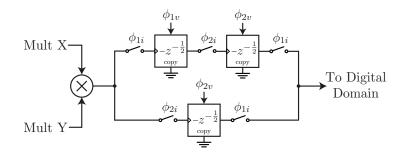

| 7.5  | Block diagram of the calculation part of the reactive power measure-                                                                                           |   |

|      | ment system                                                                                                                                                    | ) |

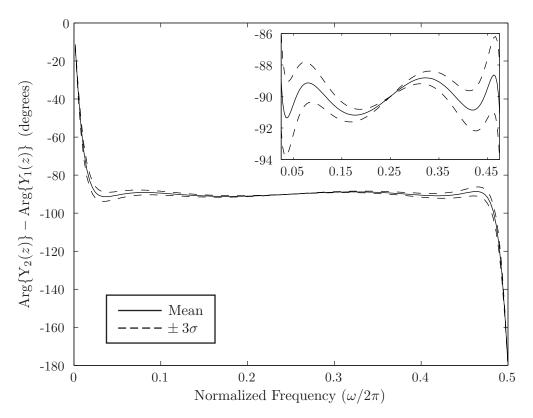

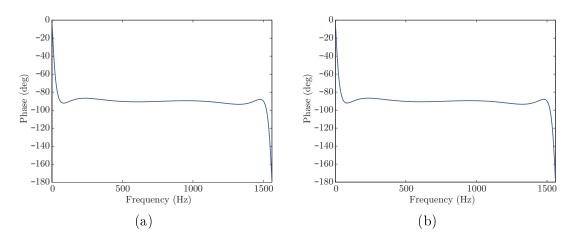

| 7.6  | Phase plot of the frequency response of the (a) top and (b) bottom                                                                                             |   |

|      | path                                                                                                                                                           | ) |

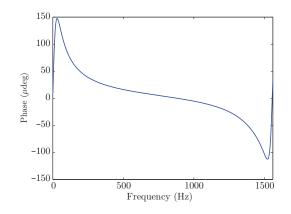

| 7.7  | Phase difference between top and bottom path                                                                                                                   |   |

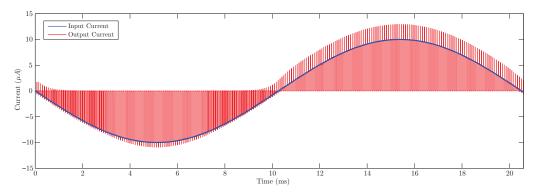

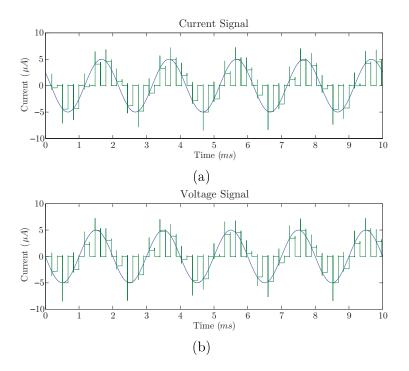

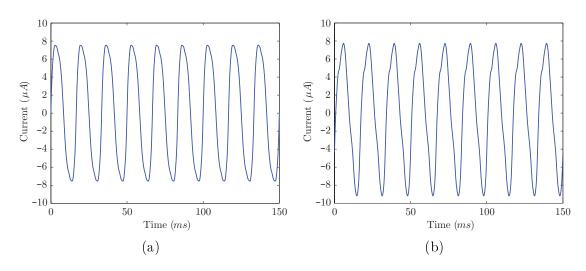

| 7.8  | Continuous-time and sampled representation of the (a) current input                                                                                            |   |

|      | signal and (b) voltage input signal                                                                                                                            | 2 |

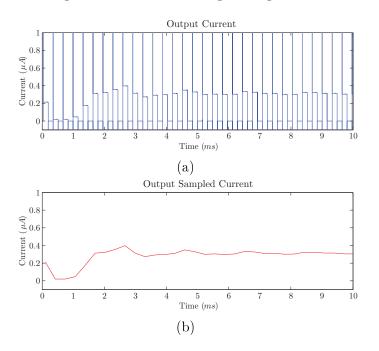

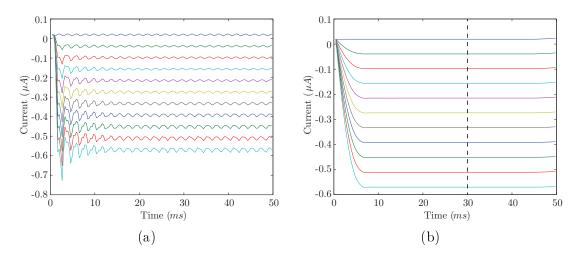

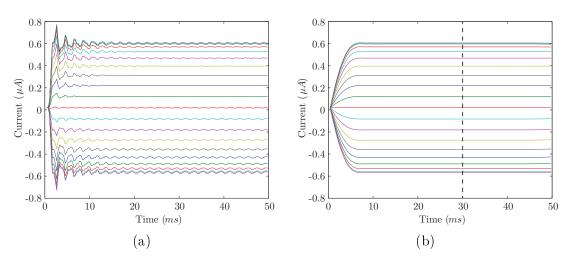

| 7.9  | Reactive power measurement system output result. (a) Output cur-                                                                                               |   |

|      | rent proportional to reactive power and (b) sampled representation 112                                                                                         | 2 |

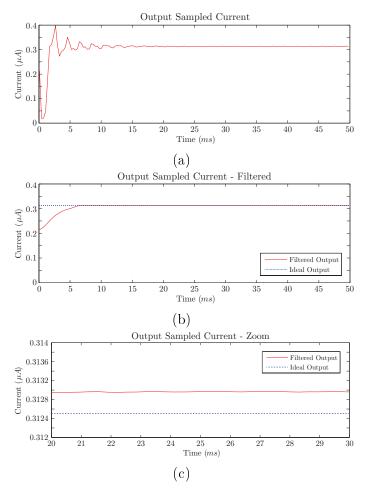

| 7.10 | (a) Sampled representation, (b) sample representation filtered and (c)                                                                                         |   |

|      | sample representation filtered zoomed                                                                                                                          | 3 |

| 7.11 | Different circuit outputs for a $I_{volt} = 5\mu A$ and $\varphi = 30^{\circ}$ . (a) Sampled                                                                   |   |

|      | output and (b) Filtered output with the points under the dashed line                                                                                           |   |

|      | $(30 \text{ ms})$ selected for next plots. $\dots \dots \dots$ | 1 |

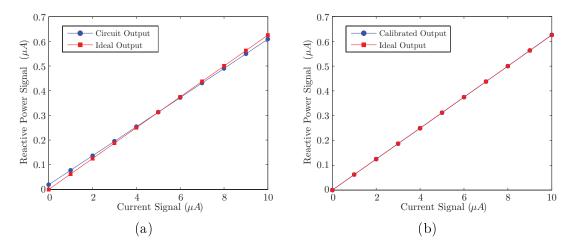

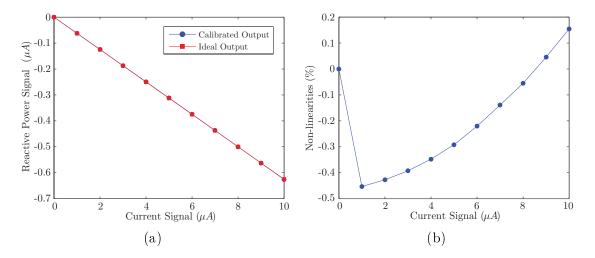

| 7.12 | Reactive power signal vs. current signal level for $I_{volt} = 5\mu A$ and                                                                                     |   |

|      | $\varphi = 30^{\circ}$ (a) before and (b) after calibration                                                                                                    | 5 |

| 7.13 | Non-linearity errors after calibration vs. current signal level for $I_{volt} =$                                                                               |   |

|      | $5\mu A \text{ and } \varphi = 30^{\circ}116$                                                                                                                  | 3 |

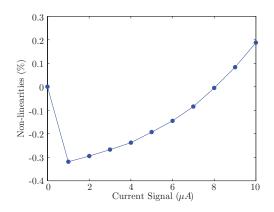

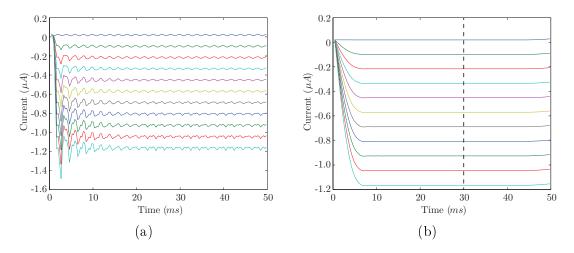

| 7.14 | Different circuit outputs for a $I_{volt} = 10 \mu A$ and $\varphi = 30^{\circ}$ . (a) Sampled                                                                 |   |

|      | output and (b) Filtered output with the points under the dashed line                                                                                           |   |

|      | (30ms) selected for next plots                                                                                                                                 | 3 |

|      |                                                                                                                                                                |   |

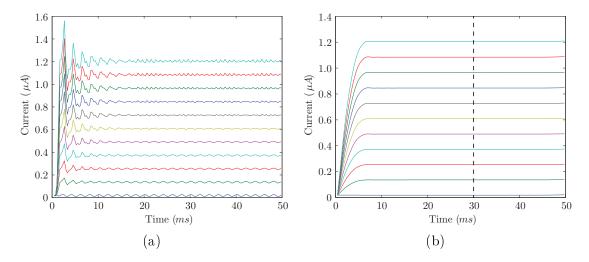

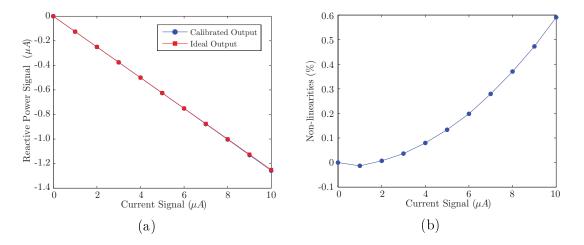

| 7.15 | (a) Reactive power signal vs. current signal level after calibration and                                                                                           |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 16 | (b) Non-linearity errors for $I_{volt} = 10\mu A$ and $\varphi = 30^{\circ}$                                                                                       |

| 1.10 | Different circuit outputs for a $I_{volt} = 5\mu A$ and $\varphi = -30^{\circ}$ . (a) Sampled output and (b) Filtered output with the points under the dashed line |

|      | (30ms) selected for next plots                                                                                                                                     |

| 7.17 | (a) Reactive power signal vs. current signal level after calibration and                                                                                           |

|      | (b) Non-linearity errors for $I_{volt} = 5\mu A$ and $\varphi = -30^{\circ}$                                                                                       |

| 7.18 | Different circuit outputs for a $I_{volt} = 10 \mu A$ and $\varphi = -30^{\circ}$ . (a) Sam-                                                                       |

|      | pled output and (b) Filtered output with the points at 30ms selected                                                                                               |

|      | for next plots                                                                                                                                                     |

| 7.19 | (a) Reactive power signal vs. current signal level after calibration and                                                                                           |

|      | (b) Non-linearity errors for $I_{volt} = 10\mu A$ and $\varphi = -30^{\circ}$                                                                                      |

| 7.20 | Different circuit outputs for a $I_{volt} = 5\mu A$ , $I_{cur} = 5\mu A$ and a variety                                                                             |

|      | of phase differences. (a) Sampled output and (b) Filtered output with                                                                                              |

|      | the points under the dashed line (30ms) selected for next plots 119                                                                                                |

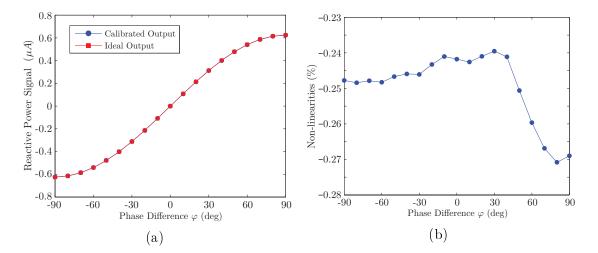

| 7.21 | (a) Reactive power signal vs. phase difference $\varphi$ after calibration and                                                                                     |

|      | (b) Non-linearity errors for $I_{volt} = 5\mu A$ and $I_{cur} = 5\mu A$                                                                                            |

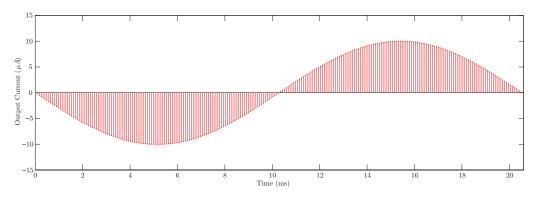

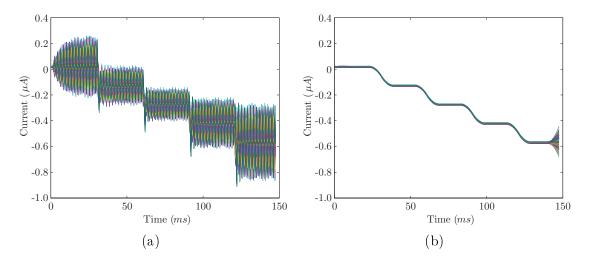

|      | (a) Voltage and (b) current non-sinusoidal input signals                                                                                                           |

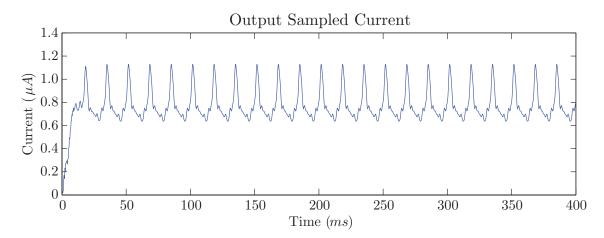

|      | Sampled output current for non-sinusoidal inputs                                                                                                                   |

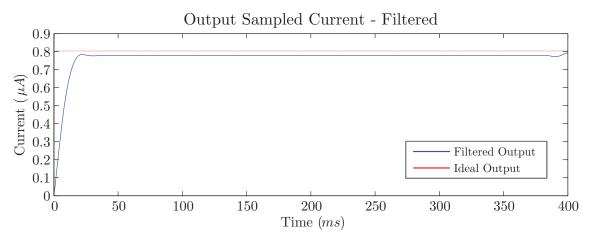

|      | Filtered output current for non-sinusoidal inputs                                                                                                                  |

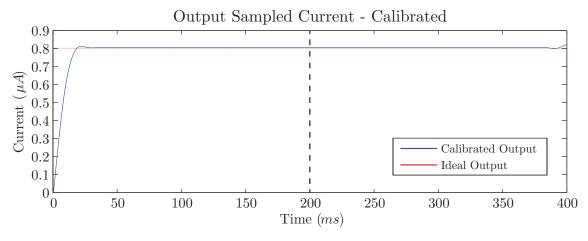

|      | Calibrated output current for non-sinusoidal inputs                                                                                                                |

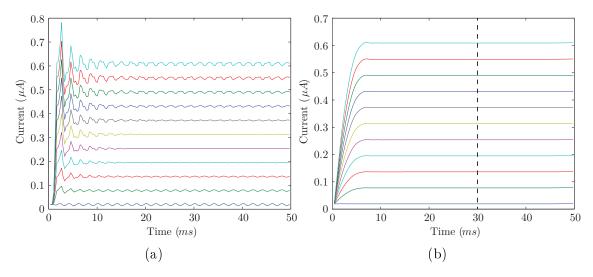

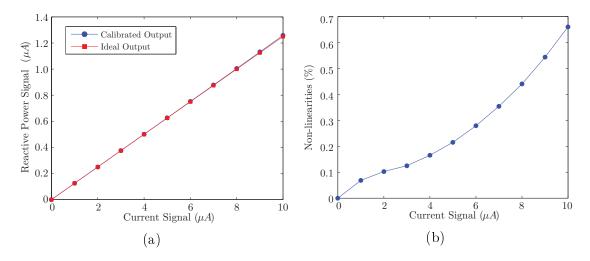

| 1.20 | Monte Carlo simulation results for a transient simulation with vari-<br>able current signal level $L_{\rm exp} = 5 \mu A$ and $(2 - 20^{\circ})$ (a) Sampled       |

|      | able current signal level, $I_{volt} = 5\mu A$ and $\varphi = -30^{\circ}$ . (a) Sampled output and (b) Filtered output                                            |

| 7.97 | Reactive power signal vs. current signal level for each Monte Carlo                                                                                                |

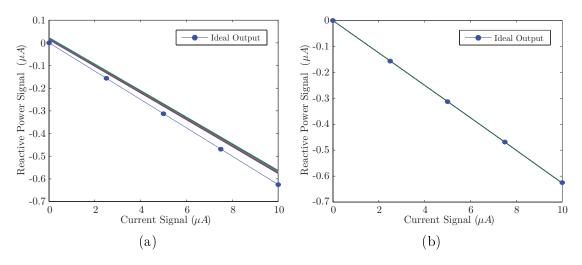

| 1.21 | sample (a) before and (b) after calibration                                                                                                                        |

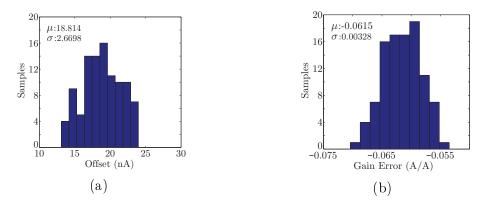

| 7.28 | Histograms for (a) offset and (b) gain error of the reactive power                                                                                                 |

|      | measurement system                                                                                                                                                 |

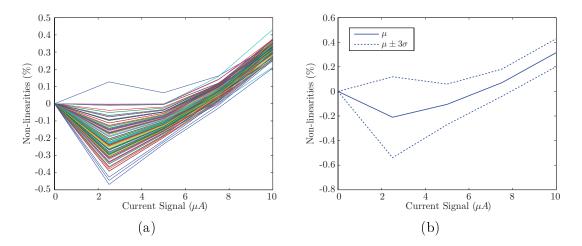

| 7.29 | (a) Non-linearity errors after calibration vs. current signal level for                                                                                            |

|      | Monte Carlo simulation and (b) statistical distribution of the non-                                                                                                |

|      | linearity errors                                                                                                                                                   |

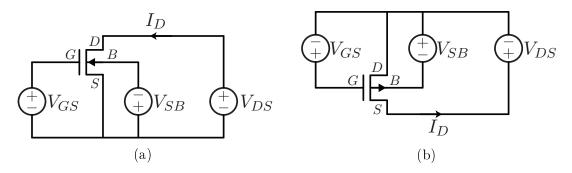

| A.1  | MOS transistor symbol. (a) NMOS and (b) PMOS                                                                                                                       |

| B.1  | Wide swing cascode current mirror circuit                                                                                                                          |

| B.2  | Differential pair circuit                                                                                                                                          |

| B.3  | Current squarer circuit                                                                                                                                            |

|      |                                                                                                                                                                    |

| C.1 | Block representation of an ideal current memory cell (a) and a Zero-      |

|-----|---------------------------------------------------------------------------|

|     | voltage switching current memory cell (b). A cascade of four ZVS-         |

|     | CMC blocks (c)                                                            |

| C.2 | Block representation of a cascade of four current memory cells $152$      |

| C.3 | Differential Current Mirror implementation                                |

| C.4 | Block representation of a differential current mirror with asymmetric     |

|     | offset errors (a) and with symmetric offset errors (b)                    |

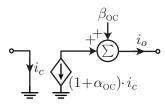

| C.5 | Block representation of an output copy current mirror                     |

| C.6 | Block diagram of a structurally all-pass section with gain error and      |

|     | offset from building blocks                                               |

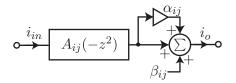

| C.7 | Equivalent block representation of a structurally all-pass section 156 $$ |

| C.8 | Block diagram of a cascade of $N_i$ structurally all-pass sections 157    |

| C.9 | Reactive power measurement system using two Hilbert transformers          |

|     | with all-pass transfer functions with gain and offset errors 159 $$       |

| D.1 | Simple current mirror circuit                                             |

| D.2 | Differential pair circuit                                                 |

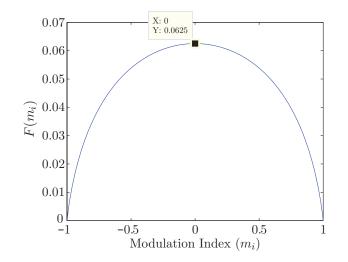

| D.3 | Plot of $F(m_i)$ vs. modulation index $m_i$                               |

| D.4 | Differential current mirror circuit                                       |

# List of Tables

| 3.1 | Characteristics of related works                                                    | 18  |

|-----|-------------------------------------------------------------------------------------|-----|

| 3.2 | Summary of systems specifications.                                                  | 28  |

| 3.3 | Input Signal Characteristics                                                        | 29  |

| 4.1 | Percentage error limits (for single-phase meters and polyphase meters               |     |

|     | with balanced loads) $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 34  |

| 4.2 | Specification summary for the utility meter.                                        | 35  |

| 5.1 | High-linearity differential pair transistor's dimensions                            | 58  |